# Simple Photonic Emission Attack with Reduced Data Complexity

Elad Carmon<sup>1</sup>, Jean-Pierre Seifert<sup>2</sup>, Avishai Wool<sup>3</sup>

<sup>1</sup> Tel-Aviv University, Tel-Aviv 69978, Israel eladca@gmail.com

<sup>2</sup> Security in Telecommunications, Technische Universität Berlin, Germany Jean-Pierre.Seifert@telekom.de

<sup>3</sup> Tel-Aviv University, Tel-Aviv 69978, Israel yash@eng.tau.ac.il

**Abstract.** This work proposes substantial algorithmic enhancements to the SPEA attack of Schlösser et al. [16] by adding cryptographic postprocessing, and improved signal processing to the photonic measurement phase. Our improved approach provides three crucial benefits: (1) For some SBox/SRAM configurations the original SPEA method is unable to identify a unique key, and terminates with up to 2<sup>48</sup> key candidates; using our new solver we are able to find the correct key regardless of the respective SBox/SRAM configuration. (2) Our methods reduce the number of required (complex photonic) measurements by an order of magnitude, thereby shortening the duration of the attack significantly. (3) Due to the unavailability of the attack equipment of Schlösser et al. [16] we additionally developed a novel Photonic Emission Simulator which we matched against the real equipment of the original SPEA work. With this simulator we were able to verify our enhanced SPEA attack by a full AES recovery which uses only a small number of photonic measurements.

#### 1 Introduction

## 1.1 Background

While the phenomena of photonic emission from switching transistors in silicon is actually a very old one, cf. [5,14], the role of photons in cryptography as a practical side channel source has just recently emerged as a novel research direction, cf. [16,11,10,17,3]. Thus, it is important to include photonic side channels in future hardware evaluations of security ICs.

However, so far only the first steps within this direction have been successfully achieved: The work of [16, 11, 10, 17, 3], showed that the required equipment to carry out successful SPEA or DPEA against real world ICs is comparable in price to that of normal Power Analysis equipment.

This is where the current paper fits in and continues the current state of the art in a better understanding of the Photonic Side Channel. It takes the next step by precisely characterizing a very low number of selected plaintexts as required for the respective photonic measurements and also relating the resulting measurements in terms of their SNR to the eventual workload of the final cryptographic key reconstruction phase.

#### 1.2 Related Work

Photonic emission in silicon is a known physical phenomena which has been studied since the 1950s [14]. Specifically in the failure analysis community, hot-carrier luminescence has primarily been used to characterize implementation and manufacturing faults and defects [8, 18]. Here, the technologies of choice to perform backside analysis are PICA (Picosecond Imaging Circuit Analysis) [1] and SSPDs (Superconducting Single Photon Detectors) [19]. Both technologies are able to capture photonic emissions with high performance in their respective field, but carry the downside of immense cost and complexity.

One of the first uses of photonic emissions in CMOS in a cryptographic application was presented in 2008 [9]. However, the authors increased the voltage supply to 7V operating voltage, which is above the chips maximum limit for voltage. The authors utilize PICA to spatially recover information about binary additions related to the AddRoundKey operation of AES running on a  $0.8\mu m$ PIC16F84A microcontroller. As the authors state, such a PICA device "is available in several laboratories, for example, in the French space agency CNES". Employing PICA in this manner led to enormous acquisition times. This is especially true considering the size of the executed code. It took the authors 12 hours to recover a single potential key byte [9]. In 2011, an integrated PICA system and laser stimulation techniques were used to attack a DES implementation on an FPGA [7]. The authors proved that the optical side channel might be used for differential analysis. However, the analysis strongly relied on a specific implementation of DES in which registers were always zeroed before their use. The results required a differential analysis and a full key recovery was also not presented. As the authors note, the use of equipment valued at more than 2,000,000 Euros does not make such an analysis particularly relevant.

Nevertheless, recently, a real breakthrough was achieved by [16,17]. This work presented a novel low-cost optoelectronic setup for time- and spatially resolved analysis of photonic emissions. The authors also introduced a corresponding methodology, named Simple Photonic Emission Analysis. They successfully performed such analysis of an AES implementation and were able to recover AES-128 keys by monitoring memory accesses. This work was also extended to AES-192 and AES-256 [17]. The same research group also introduced Differential Photonic Emission Analysis and presented a respective attack against AES-128 [11]. They successfully revealed the entire secret key with their DPEA. In 2015 Bertoni et al. [3] offered an improved Simple Photonic Emission Analysis, monitoring a different section of the SRAM logic. However, they assumed a specific SRAM structure which contains only singe byte in every row. Their simulations do not model the physical environment but rather an ideal model in which the value of every bit can be identified. They also described an attack of masked

AES, however the attack is unrealistic since it assumes monitoring the photonic emission of a single experiment.

A side channel analysis using memory access patterns is reminiscent of the field of cache attacks. For instance, the first "real world" cache- based chosen plaintext attack on AES was carried on an OpenSSL implementation [2].

#### 1.3 Contributions

In this work we enhance the original SPEA attack of Schlösser et al. [16] by adding cryptographic post-processing and an improved signal processing to the measurements phase. We call the resulting attack Enhanced SPEA, or E-SPEA for short.

Our first contribution is to record the photonic side-channel leaks from the first two AES rounds, covering 32 SBox activations. We show that these leakages embed enough constraints to allow the identification of the complete key, regardless of the placement of the SBox array in SRAM. This is in contrast to the original SPEA, which terminates with up to  $2^{48}$  key candidates for certain SRAM configurations. Furthermore, taking advantage of the slow diffusion properties in the first AES round, we are able to mount this attack very efficiently, with a time complexity of  $2^{19}$ . Our optimized cryptographic solver finds the correct key within minutes on a standard PC.

Next, we devise a strategy for choosing optimal plaintexts, that causes the photonic side-channel to produce constraints (specific SRAM accesses) which enable our solver to work very quickly for all SRAM configurations. We collect the necessary constraints with only 32 plaintexts, instead of the 256 plaintexts required by Schlösser et al. [16].

Moreover, we developed a special signal-processing decoder that automatically calibrates certain internal thresholds — relying on our chosen plaintext strategy. The decoder works even when the SNR is low, adjusting its thresholds differently to match the requirements of the cryptographic solver. To do so, the decoder uses a different (auto-calibrated) threshold for each AES round. Using the combination of our carefully crafted decoder and solver, we can trade off the number of measurements against the solver's running time: fewer measurements (i.e., a lower SNR) cause a longer running time — but without missing the correct key.

Also, in order to validate our attacks we built a Monte-Carlo simulator of the underlying physics of the photonic emissions, with a noise model which incorporates

- internal noise within the detector,

- external noise from nearby transistors, and

- other effects.

We validated our simulator against the results as reported in Schlösser [15]. Our simulator can be used to explore alternative lab setups, taking into account

various critical parameters such as the lens area, height above the chip, supply voltage, ambient temperature, and equipment sensitivity.

The combination of the above contributions provides two main benefits.

- 1. We are always able to quickly find the correct key, regardless of the SRAM configuration.

- 2. Our methods reduce the number of required *optical* measurements dramatically by an order of magnitude, and thus we are able to shorten the duration of the attack significantly.

We also believe that our photonic emission simulator is of independent interest and is of great value for the research community lacking (so far) the optical equipment as described within Schlösser [15].

**Organization.** The organization of the present paper is as follows. Section 2 introduces the SPEA attack on AES. Section 3 describes our cryptographic solver. Section 4 describes our photonic emission simulator. Section 5 explains our choice of plaintexts. Section 6 describes the Auto-calibrating decoder. Section 7 describes our performance evaluation, and we conclude in Section 8. In the appendix we describe the AES encryption process until the second SubBytes operation.

#### 2 The Photonic Side Channel in AES

#### 2.1 The SRAM and its use in AES

SRAM is a common type of volatile memory found in many ICs. The SRAM is built from memory cells arranged in rows and columns, and every memory cell can be approached using a row/column access logic. In particular, the access logic for each SRAM row includes a so called row-access transistor, which is activated whenever the IC needs to access any cell in that SRAM row. Due to to this functionality, i.e., enabling an entire row, the respective row-access transistor is very strong. This means that the photonic emission of this transistor is by magnitudes larger than the individual SRAM cells by itself. For a thorough introduction into SRAM and its physical implementation details we refer the reader to [21].

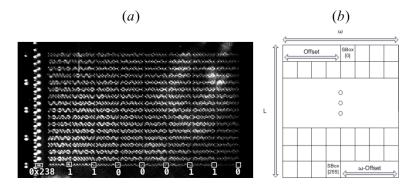

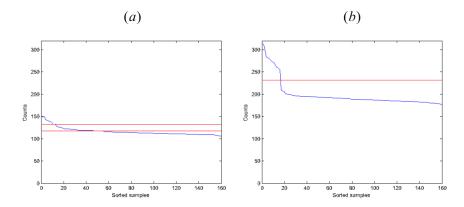

The number of bytes in an SRAM row depends on the underlying SRAM architecture. In [16] the authors found that on an AT-Mega328P a single SRAM row consists of 8 bytes, whereas an ATXMega128A1 stores 16 bytes in an entire row. Figure 1 (a) shows a photo of the SRAM, with a row width of 8 bytes.

A central component of the AES cipher is the SBox. This is an array of 256 bytes which is most often implemented as a lookup table. In each AES round the algorithm performs 16 SBox lookups. In many ICs implementing AES in software the entire SBox array is placed in SRAM.

In this paper we will denote the SRAM row width by  $\omega$ . In general the SBox starts at an *offset* within an SRAM row,  $0 \le \text{offset} \le \omega - 1$ , and occupies

**Fig. 1.** The SRAM memory in (a) captured with a CCD by the courtesy of [16]. The row-access transistors appear to the left of the SRAM cells. In (b), a schematic of the SRAM section containing the SBox in L rows,  $\omega$  cells per row and starting at some offset value.

$L = \lceil 256/\omega \rceil$  rows (see Figure 1 (b)). When  $\omega = 8$ , depending on the offset, we have L = 32 or L = 33. As we shall see, the value of the offset has an impact on the SPEA attack.

# 2.2 Simple Photonic Emission Analysis (SPEA)

Monitoring the access patterns to the SRAM rows allows the SPEA attack as presented in [16]. Towards this goal, [16] first used a simple CCD camera approach to initially map the respective IC's layout, locating the SRAM memory, and specifically, the memory rows containing the SBox array and the offset value, cf. [13]. Hereafter, they placed a NIR (Near Infra Red) photon detector offering time resolved measurements over the row access transistor of some SRAM row containing SBox values. We call the SBox row on which the detector is placed the detectable row, and denote its number by d ( $1 \le d \le L$ ). The authors ran the AES algorithm M times (by actually resetting the IC M times), encrypting the same plaintext. Consider one of the 16 SBox activations of the first AES round for plaintext byte  $p_i$  and key byte  $k_i$ . If the detector identifies an activation for SBox( $p_i \oplus k_i$ ), then there are  $\omega$  options for  $p_i \oplus k_i$  and since the plaintext is known, they have  $\omega$  options for  $k_i$ .

Using all possible plaintext bytes  $\{0,1,\ldots,255\}$  (M times each) they revealed sets of  $\omega$  potential candidates for every byte of the key, then they analyzed each key byte separately, intersecting sets of candidates for every key byte reducing the number of potential candidates. The success of the SPEA method depends on two factors:

- 1. Using a large enough number of measurements M, providing a sufficient SNR.

- 2. The offset value. The SPEA attack works best when the offset is odd. In other cases its performance is limited, and in particular when offset = 0 the

number of candidates for every key byte can't be reduced below  $\omega$  candidates for each byte, resulting in  $\omega^{16}$  key candidates.

#### 3 The E-SPEA Attack

Our attack depends on several ideas:

- 1. Use the lab setup of [16], with a NIR photon detector placed over the row access transistor of some row d in the SBox, to record the photonic emissions from the SBox activations in 2 full AES rounds and use the dependence between rounds to identify the correct key.

- 2. Use a careful choice of plaintexts to quickly reduce the entropy.

- 3. A novel auto-thresholding method, based on the choice of plaintexts, lets us avoid the need to calibrate and lets us handle noise.

During the AES encryption process, there are ten rounds, each accessing SRAM memory to use the SBox array. In every round 16 bytes of the current state matrix are replaced by 16 bytes copied from the SRAM memory using the SBox as a lookup table.

Following [16] we place a detector over the location of the transistor controlling access to a row of SRAM containing  $\omega$  cells of the SBox array. Thus each of the 16 SBox accesses per AES round has a  $\approx 1/L$  probability that the row on which the detector is located ("the detectable row") will be accessed, assuming a random plaintext. Our attack requires knowing the offset value (recall Figure 1 (a)) and the row number (d) of the detectable row.

#### 3.1 The Attack Structure

The attack activates the AES IC to encrypt plaintexts of the form  $\{a, a, \ldots, a\}$  (all plaintext bytes are the same) for different values of a. For each key byte  $k_j$ , if the detectable row is accessed in the first AES round while looking up state byte j in the SBox, we obtain a constraint on the possible value of  $k_j$ , which reduces the number of possibilities for its value from 256 to  $\omega$ . In [16] the authors iterated over all 256 plaintext options, guaranteeing that the detectable row is accessed at least once for every key byte in the first AES round (in Section 5 we show that we can achieve the same with much fewer plaintexts). Thus we obtain at most  $\omega^{16}$  AES key candidates based only on constraints from round 1 one of which is the correct key. When  $\omega=8$  we get  $\omega^{16}=2^{48}$ .

Now we can use the detected leakage from round 2 to identify the correct key and discard the false ones. For a fixed plaintext and a given key candidate, we can deterministically compute the  $2^{nd}$  round key and the state at the end of round 1. We can then deduce the 16 SBox cells that are accessed in round 2 and compare them to the access pattern measured by the detector. The probability of matching the detected pattern is  $\omega^{16}/2^{128}$ . Therefore, for the  $\omega^{16}$  candidates from round 1, we can expect  $\approx \omega^{32}/2^{128}$  candidates to fit the leakage from both

rounds. For  $\omega = 8$  we get  $\approx 2^{96}/2^{128} \ll 1$ , so it is very likely that we will find just the single correct key.

Note that the above process is a naive method used only to illustrate that the leakage from the first two AES rounds is sufficient to uniquely identify the correct key. However, we can do much better: We devised a specialized solver that has a time complexity of  $2^{19}$  and space complexity of  $2^{23}$  bits, when  $\omega = 8$ .

#### 3.2 The solver

Let a partial key be an array of 16 cells, each of which may contain either a value 0...255 or 'undefined'. The main algorithm maintains a set of partial key candidates, and works in stages. Each stage corresponds to a particular state byte, or a set of state bytes, in round 2: In the stage for state byte j the algorithm first grows the set of candidates, by extending each candidate partial key so all the key bytes that state byte j depends on are well defined. Then the algorithm rejects all the (extended) candidates that are inconsistent with  $2^{nd}$  round leaks. A stage can correspond to several state bytes if the extended candidate keys are well defined for all the depended-upon key bytes of the stage. The pseudo-code for a single stage has the following structure:

```

//stage for state byte j input: set prevCandidates

Let enumBytes(j) be the set of additional key bytes that state byte j depends on and are still 'undefined' in all partial keys in prevCandidates.

```

```

1: for all C in prevCandidates do

2: for all possible values V for key bytes in enumBytes(j) do

3: if Consistent (j, C||V) then

4: nextCandidates \leftarrow nextCandidates \cup {C||V}

5: end if

6: end for

7: end for

8: prevCandidates \leftarrow nextCandidates

9: nextCandidates = \emptyset

```

We keep the results of the  $2^{nd}$  round row activations in a data structure denoted by R2A: R2A $\{p^t\}$  is a vector of L bits such that  $(R2A\{p^t\})_j = 1$  if plaintext  $p^t$  caused a detectable SBox access in round 2 on state byte j.

For a given partial key X and state byte  $1 \le j \le 16$  line 3 calls a function to test whether X is consistent with the  $2^{nd}$  round leaks for state byte j:

$$\begin{bmatrix} k_{1} & \cdot & \cdot & * \\ * & k_{6} & \cdot & k_{14} \\ * & \cdot & k_{11} & * \\ * & \cdot & \cdot & k_{16} \end{bmatrix} \qquad \begin{bmatrix} k_{1} & \cdot & \cdot & * \\ * & k_{6} & \cdot & * \\ k_{3} & \cdot & k_{11} & * \\ * & \cdot & \cdot & k_{16} \end{bmatrix}$$

**Fig. 2.** The key bytes affecting the round 2 SBox accesses: (a) for state byte 1, (b) for state byte 3. Note that the key bytes on the diagonal (1,6,11,16) determine the state bytes of the  $1^{st}$  column at the end of round 1, and the key bytes on the left and right columns determine the  $2^{nd}$  round key.

```

1: Consistent (j, X)

2: for all plaintexts p^t do

3: v_{jt} \leftarrow \text{RowLookupOf } (j, X, p^t)

4: if ((v_{jt} == d \text{ and } (\text{R2A}\{p^t\})_j == 0) \text{ or } (v_{jt} != d \text{ and } (\text{R2A}\{p^t\})_j == 1)) then

5: return FALSE //partial key X is inconsistent

6: end if

7: end for

8: return TRUE //partial key X is consistent

```

The function RowLookupOf  $(j, X, p^t)$  at line 3 returns the SBox row that is looked up for state byte j with plaintext  $p^t$  and partial key X. We ensure that all the key bytes that state byte j depends on are well defined in X by a careful ordering of the enumeration (see below), that also ensures the algorithm's ability to disqualify partial keys early. The time complexity of Consistent (j, X) is clearly  $O(N_p)$ , where  $N_p$  is the number of plaintexts.

#### 3.3 Selecting the Enumeration Order

According to appendix A, state byte 1 depends on key bytes 1,6,11,16 after the round 1 MixColumns step, and byte 1 of round key 2 depends on key bytes 1,14. Thus immediately before the SBox lookup of round 2, state byte 1 depends on 5 key bytes: 1,6,11,14,16. (see Figure 2a). So in the solver's stage 1 we enumerate over a set of  $\omega^5$  candidates. The consistency check will reduce the set to about  $\frac{\omega^5}{L} \approx 2^{10}$  candidates. In the same way we find that state byte 3 depends on key bytes 1,3,6,11,16— 4 of which we've already enumerated in stage 1 (see Figure 2b). So we only need to extend each candidate partial key by a single byte. Thus we enumerate on byte 3 for the second stage. After this stage the number of candidates becomes  $\approx (\frac{\omega^5}{L}) \cdot \omega \cdot \frac{1}{L} = \frac{\omega^6}{L^2}$ , which is  $2^8$  when  $\omega = 8$ .

Continuing in a similar manner, we find that state byte 2 depends on 6 key bytes: 1,2,6,11,15,16 so we need to extend the partial keys by 2 bytes (2 and

| Stage | Column | State byte  | Bytes enumarated | Candidates                      | Running complexity | Space<br>(bits)             |

|-------|--------|-------------|------------------|---------------------------------|--------------------|-----------------------------|

| 1     |        | 1           | 1,6,11,14,16     | 215                             | 218                | $5\cdot 2^3\cdot 2^{15}$    |

| 2     | 1      | 3           | 3                | $2^{10} \cdot 2^3$              | 216                | $6 \cdot 2^3 \cdot 2^{13}$  |

| 3     | 1      | 2           | 2,15             | 28 · 26                         | 217                | $8\cdot 2^3\cdot 2^{14}$    |

| 4     |        | 4           | 4,13             | 29 · 26                         | 218                | $10 \cdot 2^3 \cdot 2^{15}$ |

| 5     | _      | 5,6         | 5,10             | $2^{10} \cdot 2^{6}$            | 219                | $12 \cdot 2^3 \cdot 2^{16}$ |

| 6     | 2      | 7           | 7                | 2 <sup>6</sup> · 2 <sup>3</sup> | 212                | $13 \cdot 2^3 \cdot 2^9$    |

| 7     |        | 8           | 8                | $2^4 \cdot 2^3$                 | 210                | $14\cdot 2^3\cdot 2^7$      |

| 8     | 3      | 9,10,11     | 9                | $2^2 \cdot 2^3$                 | 2 <sup>8</sup>     | $15 \cdot 2^3 \cdot 2^5$    |

| 9     |        | 12          | 12               | $2^{-10} \cdot 2^3$             | 2-4                | $16 \cdot 2^{3}$            |

| 10    | 4      | 13,14,15,16 | -                | $2^{-27}$                       | 2-24               | $16 \cdot 2^{3}$            |

**Fig. 3.** The algorithm going over bytes of the second round state matrix column by column. For every stage of the solver the number of candidates increases due to the newly enumerated key bytes— but the number of remaining candidates after the stage is reduced due to the second round constraints. This analysis assumes one second round activation for each of the state matrix byte j, and  $\omega = 8, L = 32$ , thus each stage cuts down the number of candidates by a factor of  $2^5$ .

15), ending the stage with  $\frac{\omega^8}{L^3} = 2^9$ , and so forth column by column. Figure 3 illustrates the whole process. The figure shows that stage 5 dominates the time complexity (of  $2^{19}$ ) and space complexity (of  $2^{21}$ ).

Note that the state bytes of the first column (state bytes 1-4) collectively depend on 10 key bytes. A simpler algorithm would have enumerated over all 10 bytes together. However, such an approach would have had a time complexity of  $\omega^{10}=2^{30}$  (for  $\omega=8$ )— significantly worse than the time complexity of our stages 1-4 combined.

# 4 The Photonic Emissions Simulator

The probability of detecting an SRAM row access consists of the probability for a photon generation, the probability for the photon to emit into the detection area of the detector and the system overall efficiency factor.

The overall probability is very low (as stated in [16]) and therefore a large number of measurements (M) is needed. We wrote a Monte Carlo simulation [4] in order to investigate the effect of using different numbers and different kinds of plaintexts, placing the detector in different locations, changing physical parameters in the setup and assessing the number of measurements that needs to be done in order to reach a sufficient SNR to extract the correct key.

The rate of photon emission is proportional to the number of electrons found in the channel of the MOSFET transistor and the probability for each electron to emit a photon [20]. The rate of emitted photons per second in a transistor can be calculated based on the equation [20, 15]:

$$N_{ph} = \alpha \frac{J_{DS}}{q} (V_{DS} - V_{DS,sat}) exp(-\frac{\beta \Delta L}{V_{DS} - V_{DS,sat}})$$

(1)

where  $\alpha$  is an efficiency constant, depending on the semiconductor technology and in particular the doping level of the transistor,  $J_{DS}$  is the drain-source current, q is the electron charge,  $V_{DS}$  is the drain-source voltage of the transistor,  $V_{DS,sat}$  is the drain-source voltage at saturation,  $\beta$  is a constant of the transistor and  $\Delta L$  is the length of the high field region which is roughly the length of the pinch-off region of the transistor.

The probability for an emitted photon to be found in the detection area is:

$$P_{Area} = \frac{A}{4\pi R^2} \tag{2}$$

where A is the detection area and R is the distance between the detector and the transistor.

The overall system efficiency includes the efficiency of the optical lenses and fiber optics  $(D_{\rm eff})$ , and the photon detection efficiency (PDE) which defines the probability of a successful photon detection for the specific detector [15]. Thus the rate of detected photons is:

$$N_{ph} \cdot P_{Area} \cdot \text{PDE} \cdot D_{\text{eff}}$$

(3)

In [16, 15] the authors did not specify the precise values of all the parameters of equation (1). Instead they supplied an empirical estimate of  $N_{ph}$  for their lab setup:  $4.5 \times 10^{-2}$  emitted photons per SBox activation. Our simulation uses their estimation:

$$N_{sim} = 4.5 \times 10^{-2} \cdot P_{Area} \cdot PDE \cdot D_{\text{eff}} \tag{4}$$

we use equation (1) only to investigate the effect of changing the voltage, or the current, of the transistor.

According to [15] an SRAM access during the first round of AES occurs once every  $\approx 800$ ns and all 16 accesses are presented in a 13000ns trace. The authors measured the duration of the photonic emission during an SRAM row access to be 3.5ns and sampled the row access transistor every 20ns giving a bandwidth of  $\Delta f = 25 \mathrm{MHz}$ .

The noise factors in the simulation are as follows:

- 1. Photons emitted from other simulated circuitry of the IC  $(N_{noise-photons})$ . The number of counted detections generated by these photons is small due to spatial separation causing an angle towards the location of the detector that decreases the effective detection area by a factor of  $R/\sqrt{R^2+x^2}$  where x is the horizontal distance between the transistor and the location of the detector

- 2. Thermal noise— the detector works by measuring the voltage drop over some resistor, whose behavior is affected by the temperature. The current developed on the detector caused by thermal noise is:

$$\langle J_{th} \rangle^2 = \frac{4K_B T \Delta f}{R_{det}} \tag{5}$$

Where  $K_B$  is the Boltzmann constant,  $\Delta f$  is the bandwidth of the detector, T is the temperature (Kelvin) and  $R_{det}$  is the resistance of the detector

| Detector   | PDE(%), λ (nm) | DZR       | Δf (MHz) | D_eff | $A(\mu m^2)$ | R(µm) | T (K) |

|------------|----------------|-----------|----------|-------|--------------|-------|-------|

|            |                | (1/sec)   |          |       |              |       |       |

| InGaAs/InP | 25 @ 1550      | 1.2 · 105 | 25       | 10%   | 50           | 25    | 250   |

| SPAD       | -              |           |          |       |              |       |       |

Fig. 4. The details of the detector used in [16] taken from [15].

estimated to be  $R_{det} = 100\Omega$  based on [15]. Using equation (5) we get that the number of thermal noise detections is  $N_{th} = a \langle J_{th} \rangle / q$  where a is the ratio between the number of photons to the number of electrons and was estimated to be  $2.3 \times 10^{-5}$  by [12,15] and q is the elementary charge. Note that the temperature listed in figure 4 (T=250K) is not an error: the detector used in [15,16] was cooled down to this low temperature (-23C) precisely to reduce the thermal noise.

3. Shot noise  $(N_{shot})$  caused by the quantum nature of light. Shot noise depends on the emitted photons frequency and the temperature [15]. In our simulator we used the following formula:

$$N_{shot} = \frac{\overline{N}}{\overline{n}} \Delta n \tag{6}$$

which is a simplified equation assuming an ideal detector [15] and where  $\overline{n}$  is the mean photon count,  $\Delta n$  is the photon count and  $\overline{N}$  is the electrons mean count (again can be estimated using the ratio a).

4. Dark count (DZR)- an additive noise of detection events not initiated by photons but from other processes inside the detector such as tunneling [15].

Therefore, the number of noise detections is:

$$N_{noise} = N_{noise-photons} + N_{shot} + N_{th} + DZR \tag{7}$$

Using equations (4),(7) and the values from Figure 4 gives us the expected number of detected photons for an SRAM row access  $\approx 5.7 \times 10^{-5}$ , and the expected number of noise counts per sample in our model is  $\approx 3 \times 10^{-5}$ .

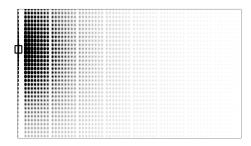

The simulation contains a simplified SRAM structure of ATmega328P IC as described in [16] and the simulation was calibrated based on the setup explanation presented in [16, 15]. The rate of photons generation was calculated based on equation (4) using the data in [15] and was found suitable with the results presented in [6, 12]. Figure 5 shows the simulated rate of detected photons from various transistors in the SRAM structure, illustrating its row structure.

# 5 Choosing the Plaintexts

As stated in Section 3 when a row access is detected in round 1, the number of key candidates for that byte is reduced to  $\omega$ . The SBox values are located over L sequential rows of the SRAM memory, so the probability to observe a row access for randomly chosen plaintext is  $\approx 1/L$ .

**Fig. 5.** Simulated photonic emissions received by the detector (in a box) from the various transistors of the simulated SRAM structure over 1ms. The darkness of a point indicates the quantity of photons emitted from that point towards the detector.

For the set of plaintexts  $p^t = (a_t, \ldots, a_t)$  we use, we want to have at least one detectable row access in round 1 for every key byte. This can of course be guaranteed by using all 256 plaintexts, as done by [16]. However we can achieve the same result with much fewer plaintexts. For a given offset (recall Figure 1 (a)), a plaintext byte  $a_t$ , and key byte  $k_j$ , the AES SubBytes step generates an SRAM row access to row l

$$l = \left| \frac{a_t \oplus k_j + \text{ offset}}{\omega} \right| + 1 \tag{8}$$

We capitalize on this by using a " $\omega$ -jump" strategy for plain text ordering. We choose the following plain texts:

$$p^{t} = \{c + j \cdot \omega, \dots, c + j \cdot \omega\}$$

$$(9)$$

for  $c = \{0, \ldots, \omega - 1\}$ , and  $j = \{0, \ldots, L - 1\}$  for offset=0 or  $j = \{0, \ldots, L - 2\}$  for offset  $\neq 0$ . Essentially for every value of c this strategy holds the least-significant-bits fixed (e.g., the 3 LSBs for  $\omega = 8$ ) and goes over all options for the MSBs.

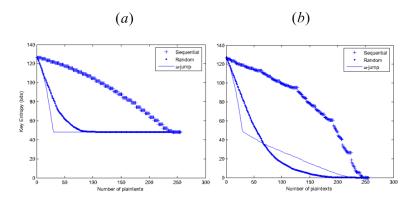

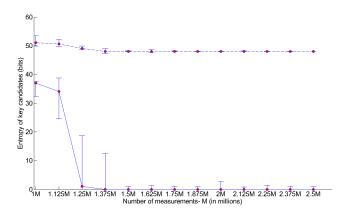

By choosing some c and going over all options of j to multiply the row width  $\omega$  we force a row access to all of the SRAM rows  $\{1,2,3,\ldots,L\}$  for offset =0 regardless of the key value k. If offset  $\neq 0$ , the " $\omega$ -jump" strategy causes a detectable row access for all the rows  $\{2,3,\ldots,L-1\}$  plus one more row access—to the first or the last row. After going over all the values of j we increment c and repeat. By setting the detectable row d to be  $2 \leq d \leq L-1$  and using a set of L (or L-1) plaintexts of equation (9) we are guaranteed to have one detectable row activation for every key byte during the first AES round. Figure 6 shows the drop in key entropy as a function of the number of plaintexts. Figure 6 (b) shows that for offset=1 the random strategy of plaintexts selection reduces the entropy to 0 quicker than the " $\omega$ -jump" strategy, but using the " $\omega$ -jump" strategy the entropy reaches the desired working point of our simulator (48 bit entropy) using only L carefully chosen plaintexts.

**Fig. 6.** The entropy of the key as function of the number of plaintexts, using only first round leakages for offset=0 (a) and offset=1 (b). The graphs show the sequential plaintext selection used in [16], a uniformly- random selection strategy and our "ω-jump" strategy. We can see that using only round-1 information, the entropy can't be reduced below 48 bit when offset=0. We can see that using "ω-jump" the entropy decreases fast and using only 32 plaintexts we have a 48bit entropy, which is the "working point" of our solver, for all offsets.

Note that unlike the first round, the second round row activations can't be controlled by the choice of plaintexts since the access pattern in round 2 also depends on the key diffusion caused by round 1.

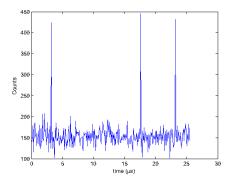

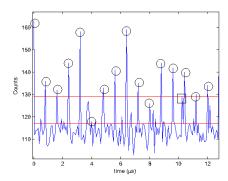

# 6 Decoding the Photonic Traces with Auto Threshold Calibration

For each of the plaintexts  $p^t$  we activate the IC (or, in our case, the simulator) M times. For each activation we count the number of detected photons per time step, while the detector is fixed at SRAM row d. We summarize the detection counts per time step, to obtain a "photonic trace"  $T(p^t)$  for each plaintext, for the time duration of the first 2 AES rounds. Following [15, 16] we assume an IC instruction cycle of 800 ns<sup>1</sup>, a photonic trace spans  $25.6\mu$ s, represented by a vector of 1280 samples, one per 20ns (see Figure 7). For plaintext  $p^t$  we now need to decode the trace to extract two arrays of 16 bits: R1A and R2A recording the results of the 2 AES rounds' SBox activations. A bit value of 1 indicates that the plaintext caused a detectable SRAM access on the current SBox activation. A natural decoding rule is to use a threshold: if the number of detected activations during SBox access j in round 1 exceeds the threshold, we set  $(R1A\{p^t\})_j = 1$ , and 0 otherwise, and similarly for R2A.

<sup>&</sup>lt;sup>1</sup> Note that this clock frequency is a slow 1.25MHz. The AT-Mega328p can operate at faster clock frequencies, up to 20MHz- we simulated the 1.25MHz clock to allow a comparison of the simulated results with the findings of [15, 16].

Fig. 7. A typical photonic trace received from the simulator, M=5,000,000. The peaks indicate a detectable access to the SBox.

A crucial task is calibrating the threshold so it can reliably distinguish between true detections and noise. Calibrating a threshold is often a heuristic trial-and-error process. However, since we choose the plaintexts in a specific way, we can calibrate the threshold automatically to its optimal value.

#### 6.1 Calibration at High SNR

Our method of choosing plaintexts guarantees a first round detectable row activation for every state byte j for at least one plaintext. Therefore we aggregate the  $N_p$  photonic traces (one per plaintext) by taking the *maximum* count per time step:

$$(maxT)_i = \max_{t=1...N_p} \{ (T(p^t))_i \}$$

(10)

for the time duration of AES round 1.

This max-trace should exhibit 16 distinct peaks, at the time-steps corresponding to the 16 SBox activations of AES round 1. If we sort maxT in descending order, we expect to see a clear drop between the  $16^{th}$  peak value, and the  $17^{th}$  (which is the highest peak caused by the noise). We can use this fact and choose our threshold to be the midpoint between the two peaks:

$$Threshold = \frac{peak_{16} + peak_{17}}{2} \tag{11}$$

where  $peak_{16}$  and  $peak_{17}$  are the 16th and 17th largest samples of maxT (see Figure 8 (b)).

Even though the threshold is calibrated on maxT for the first AES round, it is valid for every individual trace  $T(p^t)$ , and for both AES rounds. Thus we can use this threshold for all  $N_p$  traces to set the bit arrays  $R1A\{p^t\}$  and  $R2A\{p^t\}$ .

**Fig. 8.** The sorted maxT trace and the auto-calibrated thresholds (lines) for (a) M=1,500,000 and (b) M=3,750,000 measurements. We can notice on (b) a gap between the 16th and the 17th samples and the two thresholds converge.

#### 6.2 Calibration at Low SNR

When the number of measurements M for each plaintext is low, the SNR drops and the threshold calibration method of Section 6.1 starts to introduce decoding errors. We can define 2 error types:

- 1. False negative: a missed row activation (threshold was set too high).

- 2. False positive: an incorrect row activation (threshold was set too low).

We separate the discussion of the errors into two cases, for the first and second rounds of the AES process.

Recall that our solver (Section 3.2) uses the first AES round activations to reduce the number of candidates from 256 to  $\omega$  for every key byte. When a false positive occurs during the first AES round we will have more than  $\omega$  options for the key byte, since we will have  $\omega$  options for each activation. This could make the solver running time slower and cause the set of final key candidates to be larger. However, when a false negative occurs during the first AES round, we are left with 256 options for this key byte. Since the key bytes options are used to enumerate over all key options, too many options can make the solver running time unaffordable. Thus in AES round 1 we prefer to set the threshold low, and suffer occasional false positives.

Second AES round activations set constraints that the solver uses to disqualify key candidates obtained from first round leakages. A false negative during the second round would cause fewer constraints and weaker disqualifications—so the solver may end with more keys. However, a false positive would disqualify true key values. Therefore in AES round 2 we prefer to set the threshold too high, and suffer occasional false negatives.

Our solution is to use two thresholds: one for each AES round. The first threshold (Thr<sub>1</sub>) is set low in order to avoid false negative errors of first round

Fig. 9. A trace and the low and high thresholds for M=1,000,000 (low SNR). In circles, peaks at expected time slots. In a box, a peak at an unexpected time slot. Thus, Thr<sub>1</sub> is set just below the lowest circled value, and Thr<sub>2</sub> is set just above the boxed value.

activations. The second threshold (Thr<sub>2</sub>) is set higher in order to avoid second round false positives. To calibrate the thresholds we again use the max-trace maxT. We utilize the fact that we know the time-steps in which the 16 S-Box accesses occur. We use the following process to calibrate the two thresholds.

- 1. Generate the max-trace maxT as in Section 6.1.

- 2. Thr<sub>1</sub> is set to the maximal value for which  $(maxT)_i \geq Thr_1$  for all 16 timesteps i at which there is a first round activation.

- 3. Thr<sub>2</sub> is the minimal value for which  $(maxT)_i < \text{Thr}_2$  for all time-steps i at which there is no first-round activation.

If the SNR is high then peaks at the 16 true activations will be all higher than the noise— so we will get  $Thr_1 \ge Thr_2$ . In such a case we fall back to the method of Section 6.1 and set both thresholds to be  $(Thr_1 + Thr_2)/2$ .

We take key candidates based on first round activations using Thr<sub>1</sub>, and we collect the constraints from the second round activations using Thr<sub>2</sub>.

# 7 Practical Results

We implemented the photonic emissions simulator of Section 4 in Matlab. The solver was implemented in python. The experiments were run on a relatively old Intel Core Duo T2450 2GHz, 2GB RAM PC running Windows Vista. We simulated the ATmega328P IC with SRAM row width of  $\omega = 8$  and generated the plaintexts according to the " $\omega$ -jump" strategy of Section 5.

In order to evaluate the performance of our attack we performed an extensive set of experiments. All the experiments were done with  $\omega=8$ , and with either L=32 (for offset=0) or L=33 (for all other offsets). We used the " $\omega$ -jump" strategy to generate L plaintexts for each offset.

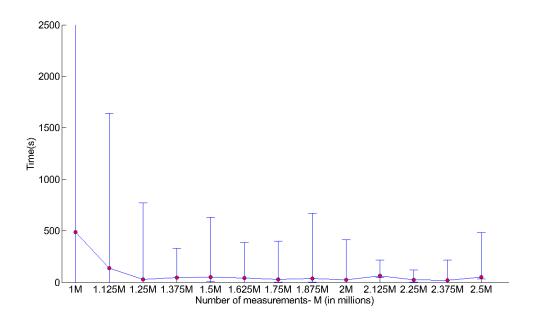

Fig. 10. The entropy of the round-1 key candidates (dashed line) and the final key candidates (solid line) as a function of the number of measurements M, for offset=0 and using different random keys and a different detector row for every test. The upper and lower bounds indicate the 5-95 percentiles and the dots mark the median values.

Fig. 11. Solver running time for different M values, for offset=0 and using different random keys and a different detector row for every test. The upper and lower bounds indicate the 5-95 percentiles and the dots mark the median values.

| Method        | Measurements (millions)   | Time (hours)                | Final key candidates                                                                                                              |

|---------------|---------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| SPEA          | 256 plaintexts * 5M=1280M | 256 plaintexts * 90 sec=6.4 | $\begin{cases} 1 & for odd offset \\ 2^{48} & for offset = 0 \\ 2^{32} & for offset = 4 \\ 2^{16} & for offset = 2,6 \end{cases}$ |

| Enhanced SPEA | 32 plaintexts * 1.5M=48M  | 32 plaintexts * 54 sec=0.5  | $\begin{cases} 1 & for 75\% \\ \sim 8 & for 24\% \\ 2^{48} & for 1\% \end{cases}$                                                 |

Fig. 12. A comparison between the SPEA and our E-SPEA methods.

For each plaintext we used 100 random keys, and for each key-plaintext combination we generated between M=1,000,000-5,000,000 traces from the photonic emission simulator (Section 4), with the detector at a random row  $2 \le d \le L-1$ . We used the threshold setting of Section 6 to decode the traces, and used the solver to find the key. For each run we set a timer on the solver: if the run time exceeded 5000sec we stopped it and recorded a failure. Figure 10 shows the attack's behavior for various values of M. We can see that as long as  $M \ge 1,500,000$  the attack works well, with the median key entropy at the end of the attack dropping below 3 bits, and a single (correct) key was found in 75% of the runs. When  $M \ge 1,500,000$  the attack takes under 10 minutes, on our slow PC. The results for other offsets were similar (graphs omitted).

Figure 12 shows a comparison of our Enhanced SPEA with the original SPEA. The Figure shows that due to the reduced number of required plaintexts, and reduced number of required measurements M, our total attack time drops by an order of magnitude, from 6.4 hours down to 30 minutes- while succeeding in finding a single (correct) key in 75% of the cases- regardless of the offset. The E-SPEA method however had difficulty with 1% of the cases, not getting below  $2^{48}$  key candidates: in those cases the number of second round activations was very low and the solver reached a timeout of 5000 seconds without being able to reduce the number of key candidates.

# 8 Conclusions, Future Work and Countermeasures

In this paper we demonstrated that using cryptographic post-processing, careful plaintext selection, and better signal processing, we are able to significantly improve upon the SPEA attack of [16]. We are able to uniquely extract the correct key regardless of the offset at which the SBox is placed in SRAM. We achieve this while reducing the required number of photonic measurements by an order of magnitude, which directly implies a similar drop in the attack's time complexity. Our cryptographic solver is extremely efficient, with a time complexity of  $2^{19}$ , and extracts the key within minutes on a a rather old PC.

Following [16] we evaluated our attack assuming an SRAM row width of  $\omega = 8$ , as in the ATMega328P. However, we note that a row width of  $\omega = 16$  (as in the ATXMega128A1) would pose a harder challenge: we expect to find

$\approx \omega^{32}/2^{128} = 1$  key candidates that fit the leakage from the first two AES rounds, as opposed to the  $\approx 2^{-32}$  expected when  $\omega = 8$ . I.e., in the intermediate stages we will have many more key candidates, the run time will be longer, and the attack will terminate with more possible keys, than when  $\omega = 8$ . Conversely, if  $\omega = 32$  then our attack should become equally efficient as when  $\omega = 8$ : we can set the detector on the *column*-access transistor. We leave evaluating alternative SRAM configurations for future work.

Note also that our photonic emissions simulator allows us to test hypothetical lab setups, since we can experiment with the lens area and height above the IC, the supply voltage, the temperature, and the detector sensitivity. It would be interesting to use the simulator's results to guide the design of better future detectors.

The attack is susceptible to countermeasures such as delays and dummy operations which can obfuscate the time a photonic emission may occur. Masking also can make the attack more difficult. Memory protection countermeasures such as memory encryption or scrambling have no effect on the emission pattern, but they can make the preliminary stage of finding the SBox values inside the SRAM memory more difficult.

# References

- G. Bascoul, P. Perdu, A. Benigni, S. Dudit, G. Celi, and D. Lewis. Time resolved imaging: From logical states to events, a new and efficient pattern matching method for VLSI analysis. *Microelectronics Reliability*, 51(9):1640–1645, 2011.

- 2. D. Bernstein. Cache-timing attacks on aes. In http://cr.yp.to/papers, 2004.

- 3. Y. M. Bertoni, L. Grassi, and F. Melzani. Simulations of optical emissions for attacking AES and masked AES. In *Security, Privacy, and Applied Cryptography Engineering (SPACE)*, *LNCS 9354*, pages 172–189. Springer Verlag, 2015.

- R. E. Caffisch. Monte carlo and quasi-monte carlo methods. Acta Numerica, Cambridge University Press., 7:1-49, 1998.

- A. Chynoweth and K. McKay. Photon emission from avalanche breakdown in silicon. Physical Review, 102(2):369, 1956.

- 6. G. Deboy and J. Kolzer. Fundamentals of light emission from silicon devices. Semiconductor Science and Technology., 9:1017–1032, 1994.

- 7. J. Di-Battista, J.-C. Courrege, B. Rouzeyre, L. Torres, and P. Perdu. When failure analysis meets side-channel attacks. In *Cryptographic Hardware and Embedded Systems (CHES)*, pages 188–202. Springer, 2010.

- P. Egger, M. Grützner, C. Burmer, and F. Dudkiewicz. Application of time resolved emission techniques within the failure analysis flow. *Microelectronics Reliability*, 47(9):1545–1549, 2007.

- 9. J. Ferrigno and M. Hlavác. When AES blinks: introducing optical side channel. *Information Security*, 2(3):94–98, 2008.

- J. Krämer, M. Kasper, and J.-P. Seifert. The role of photons in cryptanalysis. In Design Automation Conference (ASP-DAC), 2014 19th Asia and South Pacific, pages 780–787. IEEE, 2014.

- 11. J. Krämer, D. Nedospasov, A. Schlösser, and J.-P. Seifert. Differential photonic emission analysis. In *Constructive Side-Channel Analysis and Secure Design*, pages 1–16. Springer, 2013.

- A. Lacaita, F. Zappa, S. Bigliardi, and M. Manfredi. On the bremsstrahlung origin of hot-carrier-induced photons in silicon devices. *IEEE Transactions on Electron Devices*, 40(3):577–582, 1993.

- 13. D. Nedospasov, J.-P. Seifert, A. Schlosser, and S. Orlic. Functional integrated circuit analysis. In *Hardware-Oriented Security and Trust (HOST)*, 2012 IEEE International Symposium on, pages 102–107. IEEE, 2012.

- 14. R. Newman. Visible light from a silicon pn junction. *Physical Review*, 100(2):700–703, 1955.

- A. Schlösser. Hot electron Luminescence in silicon structures as photonic side channel (in German). PhD thesis, Faculty of Mathematics and Natural sciences, Berlin Institute of Technology, 2014.

- 16. A. Schlösser, D. Nedospasov, J. Krämer, S. Orlic, and J.-P. Seifert. Photonic emission analysis of AES. Workshop on Cryptographic Hardware and Embedded Systems (CHES), 2012.

- 17. A. Schlösser, D. Nedospasov, J. Krämer, S. Orlic, and J.-P. Seifert. Simple photonic emission analysis of AES. *Journal of Cryptographic Engineering*, 3(1):3–15, 2013.

- L. Selmi, M. Mastrapasqua, D. M. Boulin, J. D. Bude, M. Pavesi, E. Sangiorgi, and M. R. Pinto. Verification of electron distributions in silicon by means of hot carrier luminescence measurements. *Electron Devices, IEEE Transactions on*, 45(4):802–808, 1998.

- P. Song, F. Stellari, B. Huott, O. Wagner, U. Srinivasan, Y. Chan, R. Rizzolo, H. Nam, J. Eckhardt, T. McNamara, et al. An advanced optical diagnostic technique of IBM z990 eserver microprocessor. In *Proceedings IEEE International Test Conference (ITC)*, pages 9-pp. IEEE, 2005.

- F. Stellari, F. Zappa, S. Cova, and L. Vendrame. Tools for non-invasive optical characterization of CMOS circuits. In *International Electron Devices Meeting*, 1999.

- 21. N. Weste and D. Harris. CMOS VLSI Design: A Circuits And Systems Perspective, 4/E. Pearson Education, 2010.

# **APPENDIX**

$$\begin{array}{c} \text{Plaintext} \\ (P_1 \ P_2 \ P_3 \ P_4 \ P_3) \\ P_2 \ P_4 \ P_5 \ P_4 \\ P_3 \ P_4 \ P_5 \ P_4 \\ P_4 \ P_4 \ P_5 \ P_4 \\ P_4 \ P_4 \ P_5 \ P_4 \\ P_5 \ P_5 \ P_4 \ P_4 \\ P_6 \ P_5 \ P_6 \ P_8 \ P_8 \ P_8 \ P_9 \ P_9 \ P_8 \ P_9 \ P_8 \ P_9 \ P_8 \ P_9 \ P_9 \ P_8 \ P_9 \$$

Fig. 13. The AES process until the second SubBytes operation.