# Circuits Resilient to Additive Attacks with Applications to Secure Computation

Daniel Genkin Technion danielg3@cs.technion.ac.il Yuval Ishai Technion yuvali@cs.technion.ac.il Manoj M. Prabhakaran University of Illinois mmp@uiuc.edu

Amit Sahai University of California sahai@cs.ucla.edu Eran Tromer Tel Aviv University tromer@cs.tau.ac.il

February 24, 2015

#### Abstract

We study the question of protecting arithmetic circuits against *additive* attacks, which can add an arbitrary fixed value to each wire in the circuit. This extends the notion of algebraic manipulation detection (AMD) codes, which protect *information* against additive attacks, to that of *AMD circuits* which protect *computation*.

We present a construction of such AMD circuits: any arithmetic circuit C over a finite field  $\mathbb{F}$  can be converted into a functionally-equivalent randomized arithmetic circuit  $\widehat{C}$  of size O(|C|) that is fault-tolerant in the following sense. For any additive attack on the wires of  $\widehat{C}$ , its effect on the output of  $\widehat{C}$  can be simulated, up to  $O(|C|/|\mathbb{F}|)$  statistical distance, by an additive attack on just the input and output. Given a small tamper-proof encoder/decoder for AMD codes, the input and output can be protected as well.

We also give an alternative construction, applicable to small fields (for example, to protect Boolean circuits against wire-toggling attacks). It uses a small tamper-proof decoder to ensure that, except with negligible failure probability, either the output is correct or tampering is detected.

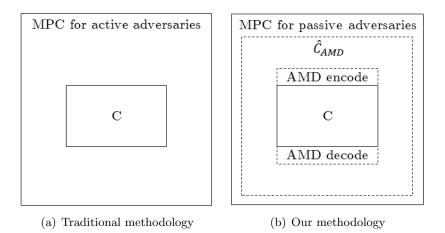

Our study of AMD circuits is motivated by simplifying and improving protocols for secure multiparty computation (MPC). Typically, securing MPC protocols against *active* adversaries is much more difficult than securing them against *passive* adversaries. We observe that in simple MPC protocols that were designed to protect circuit evaluation only against *passive* adversaries, the effect of any *active* adversary corresponds precisely to an additive attack on the original circuit's wires. Thus, to securely evaluate a circuit C in the presence of active adversaries, it suffices to apply the passivesecure protocol to  $\hat{C}$ . We use this methodology to simplify feasibility results and attain efficiency improvements in several standard MPC models.

# Contents

| 1                         | Introduction                                                      | 1  |  |  |  |  |

|---------------------------|-------------------------------------------------------------------|----|--|--|--|--|

|                           | 1.1 Overview                                                      | 1  |  |  |  |  |

|                           | 1.2 Our contribution                                              | 3  |  |  |  |  |

|                           | 1.3 Overview of techniques                                        | 7  |  |  |  |  |

|                           | 1.4 Related work                                                  | 11 |  |  |  |  |

| <b>2</b>                  | Preliminaries                                                     | 12 |  |  |  |  |

|                           | 2.1 Definitions                                                   | 12 |  |  |  |  |

|                           | 2.2 AMD codes                                                     | 13 |  |  |  |  |

| 3                         | AMD circuits over large finite fields                             |    |  |  |  |  |

|                           | 3.1 Simplifying the circuit model                                 | 14 |  |  |  |  |

|                           | 3.2 Protecting low-degree circuits over large finite fields       | 15 |  |  |  |  |

|                           | 3.3 Protecting arbitrary circuits over large finite fields        | 25 |  |  |  |  |

| <b>4</b>                  | AMD circuits over small finite fields                             |    |  |  |  |  |

|                           | 4.1 Correctness with constant error probability without a decoder | 28 |  |  |  |  |

|                           | 4.2 Improving efficiency and correctness using a decoder          | 40 |  |  |  |  |

| <b>5</b>                  | Secure MPC protocols from AMD circuits                            |    |  |  |  |  |

|                           | 5.1 Definitions                                                   | 46 |  |  |  |  |

|                           | 5.2 Secret sharing schemes and randomness extraction              | 50 |  |  |  |  |

|                           | 5.3 From general adversaries to maximal adversaries               | 52 |  |  |  |  |

|                           | 5.4 Linear-based protocols                                        | 54 |  |  |  |  |

|                           | 5.5 Security of linear-based protocols                            | 56 |  |  |  |  |

|                           | 5.6 MPC using linear-based protocols                              | 66 |  |  |  |  |

|                           | 5.7 The semi-honest BGW protocol                                  | 70 |  |  |  |  |

|                           | 5.8 The semi-honest Damgård-Nielsen protocol                      | 72 |  |  |  |  |

|                           | 5.9 The semi-honest GMW protocol                                  | 75 |  |  |  |  |

|                           | 5.10 Securing multiparty computation with preprocessing           | 81 |  |  |  |  |

| $\mathbf{A}_{\mathbf{j}}$ | ppendices                                                         | 86 |  |  |  |  |

| $\mathbf{A}$              | A MIP-based construction                                          | 86 |  |  |  |  |

| ٨                         |                                                                   |    |  |  |  |  |

|                           | Acknowledgments                                                   |    |  |  |  |  |

| R                         | References                                                        |    |  |  |  |  |

# 1 Introduction

## 1.1 Overview

The study of fault-tolerant circuits dates back to the work of von Neumann [vN56], who considered a model where every gate in a circuit can fail with some constant, and independent, probability. Subsequent works of Dobrushin and Ortyukov [DO77] and Pippenger [Pip85] showed how to construct fault-tolerant circuits in this model with only a logarithmic overhead in the worst case and a constant overhead in the typical case. Other models for fault-tolerant circuits, protecting against a bounded number of adversarial faults, were studied in [KLM94, GS95, GLM<sup>+</sup>04, IPSW06, FPV11, LL12, DK12, KLR12, DSK14].

In the present work we consider the goal of protecting boolean and arithmetic circuits against adversarial faults that may apply to *all* wires in the circuit. Even if one settles for *detecting* faults rather than fully protecting against faults, this goal would be too ambitious. Indeed, an attacker can simply rewrite the input or the output of the circuit without being detected. But there is a natural model, which is also motivated by the cryptographic applications discussed later, where achieving this goal is conceivable. In this model we limit the attacker in two ways:

- 1. The attacker cannot directly attack the input and the output to the circuit; instead, the input is fed to a small (randomized) tamper-proof input encoder and the output is obtained from a small tamper-proof output decoder.<sup>1</sup>

- 2. The class of attacks i.e., mappings from the original wire values to the new wire values is restricted.

Note that (1) alone is insufficient to remove the impossibility, since it does not rule out completely rewriting the output of the input encoder or the input to the output decoder, and (2) alone is insufficient since it does not rule out direct (albeit restricted) attacks on the input or output.

We instantiate (2) by considering *additive attacks*. That is, given a (possibly randomized) arithmetic circuit over a finite field  $\mathbb{F}$ , we allow an adversary to "blindly" add a field element of his choice to each wire in the circuit. In the case of boolean circuits, this amounts to toggling an arbitrary subset of the wires. Such additive attacks were previously considered in the context of error-correcting codes by Karpovsky and Nagvajara [KN89] and more recently by Cramer et al. [CDF<sup>+</sup>08], who constructed algebraic manipulation detection (AMD) codes which resist such attacks.<sup>2</sup> The main objective of the present work is to extend the notion of AMD codes, which protect information against additive attacks, to AMD circuits, which protect computations against such attacks.

We will start by defining a simpler notion of security against additive attacks (see Definition 1.1) that does not use any tamper-proof components (i.e., only the restriction (2) from above is used), but (inevitably) allows additive attacks on the input and output of the circuit. We show how to compile any arithmetic circuit C over a large finite field  $\mathbb{F}$  into a functionally equivalent randomized arithmetic circuit  $\hat{C}$  of size O(|C|) which is secure in this sense. The effect any additive attack has on the output of  $\hat{C}$  can be simulated, up to  $O(|C|/|\mathbb{F}|)$  statistical distance, by applying a (randomized) additive attack to the input and output alone. Thus, as far as additive attacks are concerned,  $\hat{C}$  is essentially as good as a tamper-proof implementation of C in which only the input and output are exposed.

$<sup>^{1}</sup>$ By "small" we mean independent of the circuit complexity of the function being computed (but possibly depending polynomially on the input/output size). This rules out a trivial solution where the entire computation is carried out by tamper-proof hardware.

<sup>&</sup>lt;sup>2</sup>In [CDF<sup>+</sup>08], algebraic manipulation detection codes were defined over an Abelian group, where the only manipulation allowed is an additive attack. We too are considering additive attacks, but since we work over a field (which contains a multiplication operation as well), a more appropriate term in our context would be "Additive Manipulation Detection" codes. Indeed, allowing the attacker full *algebraic* manipulation of the field elements, or even just affine attacks, would let it circumvent the security guarantee of the AMD codes of [CDF<sup>+</sup>08].

Combining the above construction with small tamper-proof encoder and decoder for AMD codes, the input and output can be protected as well. That is, any arithmetic circuit C over a large finite field can be compiled into a functionally equivalent randomized circuit of comparable size that uses small tamper-proof input encoder and output decoder, and is guaranteed to either produce the correct output of C or set an error flag, except with negligible failure probability. This construction has an additional security feature that will be useful for our motivating applications: Even in the presence of an additive attack, the field elements fed into the output decoder (and in particular the final output) reveal essentially nothing about the input x beyond C(x).

The above construction offers no security guarantees when  $\mathbb{F}$  is small. For the general case we present a more complex construction which uses small tamper-proof encoder and decoder to ensure that, except with negligible failure probability, either the output is correct or tampering is detected. More concretely, to achieve  $2^{-\sigma}$  error probability, the size of the AMD circuit  $\hat{C}$  is  $|C| \cdot \text{poly}(\sigma)$ . This construction can be used for protecting boolean circuits against wire-toggling attacks. However, here we do not realize the stronger security feature discussed above.

**Cryptographic applications of AMD circuits.** Our study of AMD circuits is further motivated by observing that they are useful for the design of protocols for *secure multiparty computation* (MPC). An MPC protocol allows two or more mutually distrusting parties to perform a distributed computation on their local inputs without compromising the secrecy of the inputs or the correctness of the outputs. Following the seminal works from the 1980s that established the general *feasibility* of secure computation [Yao86, GMW87, BGW88, CCD88, RB89], significant research efforts have been invested into studying *efficiency* questions in this area.

It is typically much easier to secure MPC protocols against *passive* adversaries, who may try to learn information about secret inputs but do not otherwise deviate from the protocol, than against *active* adversaries who may arbitrarily deviate from the protocol. The security of protocols that were only designed to withstand passive attacks may break down completely if the adversary is active. While there are general techniques for strengthening security against passive attacks into security against active attacks (most notably, the "GMW paradigm" [GMW87]), these involve a considerable overhead and do not apply at all to the type of protocols considered here.

Our key observation is that in natural MPC protocols that offer information-theoretic security against passive attacks, any cheating strategy of an active adversary can be modeled as an *additive* attack on the underlying circuit that the parties are trying to compute. This holds both for protocols in the setting of an honest majority, such as the "BGW protocol" [BGW88] and its more efficient variant from [DN07], and for protocols in the setting of no honest majority, such as variants of the "GMW protocol" over an ideal oblivious transfer oracle [GMW87, Gol04] or an OLE oracle<sup>3</sup> [IPS09].

The above observation gives rise to a novel methodology for the design of MPC protocols with security against active adversaries. Instead of designing a complex protocol for evaluating f that explicitly protects against active attacks, apply a simple protocol, which was only designed to protect against passive attacks, to evaluate an AMD circuit for f. (The role of the input encoder and the output decoder can be emulated via local computation and does not require interaction.) Thus, the most challenging aspect of MPC protocol design is reduced to the arguably cleaner problem of AMD circuit design.

We demonstrate the usefulness of this methodology by applying it to simplify and improve on previous results in the area of MPC.<sup>4</sup> For instance, we can derive the feasibility of active-secure MPC in the presence of an honest majority [RB89] from the much simpler passive-secure BGW protocol [BGW88],

<sup>&</sup>lt;sup>3</sup>An OLE oracle receives  $a, b \in \mathbb{F}$  from one party and  $x \in \mathbb{F}$  from another, and returns ax + b to the latter. OLE can be viewed as an arithmetic generalization of oblivious transfer.

<sup>&</sup>lt;sup>4</sup>Here and in the following, we allow the adversary to abort the computation and do not attempt to guarantee output delivery. This is often inevitable, e.g., when there is no honest majority, or there is an honest majority but no broadcast channel, or in security models where the adversary can block messages exchanged between honest parties (cf. [Can01]).

as well as the feasibility of active-secure MPC protocols with no honest majority [GMW87, Kil88, IPS08, IPS09] (given an OLE oracle) from their much simpler passive-secure counterparts. We also obtain a new feasibility result for MPC with no honest majority using a corruptible source of correlated randomness. On the efficiency front, we apply our methodology to a simplified variant of a passive-secure protocol from [DN07] to obtain a simpler and more efficient alternative to a recent protocol from [BF012]. We also obtain the first active-secure two-party protocol for evaluating an arbitrary arithmetic circuit over a large field using only a constant number of calls to an OLE oracle for each gate in the circuit.

#### 1.2 Our contribution

We now give a more detailed outline of our results. In Section 1.2.1 we summarize results on protecting circuits against additive attacks and in Section 1.2.2 we summarize the applications to secure multiparty computation.

#### 1.2.1 Protecting circuits against additive attacks

We start by defining our main notion of security with respect to additive attacks. Let  $f : \mathbb{F}^n \to \mathbb{F}^k$  be a function to be computed. We say that a randomized arithmetic circuit<sup>5</sup>  $\widehat{C} : \mathbb{F}^n \to \mathbb{F}^k$  is an  $\epsilon$ -secure implementation of f if  $\widehat{C}$  correctly computes f when it is not attacked, and moreover any additive attack on  $\widehat{C}$  has the same effect on the output of  $\widehat{C}$  (up to an  $\epsilon$  statistical error) as applying some additive attack to the inputs and outputs alone:

**Definition 1.1** (Additive-attack security). A randomized circuit  $\widehat{C} : \mathbb{F}^n \to \mathbb{F}^k$  is an  $\epsilon$ -secure implementation of a function  $f : \mathbb{F}^n \to \mathbb{F}^k$  if the following holds:

- Completeness. For all  $\mathbf{x} \in \mathbb{F}^n$  it holds that  $\Pr[\widehat{C}(\mathbf{x}) = f(\mathbf{x})] = 1$ .

- Additive-attack security. For any circuit  $\widetilde{C}$  obtained by subjecting  $\widehat{C}$  to an additive attack, there exists  $\mathbf{a}^{\mathsf{in}} \in \mathbb{F}^n$  and a distribution  $\mathcal{A}^{\mathsf{out}}$  over  $\mathbb{F}^k$  such that for any  $\mathbf{x} \in \mathbb{F}^n$  it holds that

$$SD\left(\widetilde{C}(\mathbf{x}), f(\mathbf{x} + \mathbf{a}^{\mathsf{in}}) + \mathcal{A}^{\mathsf{out}}\right) \leq \epsilon,$$

where SD denotes statistical distance between two distributions.

We naturally extend the definition to the case where  $f : \mathbb{F}^n \to \mathbb{F}^k$  is a randomized function. In this case completeness requires that the output distribution of  $\widehat{C}(\mathbf{x})$  and  $f(\mathbf{x})$  be identical. Finally, we say that  $\widehat{C}$  is an  $\epsilon$ -secure implementation of a circuit C if  $\widehat{C}$  is an  $\epsilon$ -secure implementation of the (possibly randomized) function f computed by C.

In Sections 3.2 and 3.3 we prove that every circuit C over a large finite field can be compiled into a circuit  $\hat{C}$  that is secure against additive attacks. Formally, we prove the following theorem.

**Theorem 1.1** (see Theorem 3.7). For any field  $\mathbb{F}$  and (possibly randomized) arithmetic circuit C:  $\mathbb{F}^n \to \mathbb{F}^k$  there exists a randomized circuit  $\widehat{C} : \mathbb{F}^n \to \mathbb{F}^k$  such that  $\widehat{C}$  is an  $\epsilon$ -secure implementation of Cwhere  $\epsilon = O(|C|/|\mathbb{F}|)$ . Moreover,  $|\widehat{C}| = O(|C|)$ .

The notion of additive-attack security in Definition 1.1 above still allows for an attack on the inputs and outputs of the circuit. This is because the adversary is allowed to attack every wire in the circuit, and in particular input and output wires. Thus, we need a randomized, *tamper-proof* input encoder Enc and output decoder Dec in order to prevent attacks against the inputs and outputs. We would like

<sup>&</sup>lt;sup>5</sup> An arithmetic circuit consists of field addition, subtraction, and multiplication gates. If it is randomized, it may also include randomness gates that output uniformly random field elements. We write  $\widehat{C} : \mathbb{F}^n \to \mathbb{F}^k$  to indicate that the input of  $\widehat{C}$  consists of *n* field elements (not including randomness gates) and its output consists of *k* field elements.

the size of Enc and Dec to be kept as small as possible (and in particular much smaller than the circuit being computed).

Notice that even in the presence of a decoder that cannot be attacked, the adversary is still allowed to attack all the wires leading from the circuit to the decoder. Thus, we cannot hope for *correcting* the result following an additive attack but must settle for a weaker guarantee of *detecting* the attack. We capture this by allowing **Dec** to have a special output, denoted *flag*, where if this output is nonzero this means that an attack has been detected.

The circuits  $\mathsf{Enc}$  and  $\mathsf{Dec}$  will perform an AMD encoding of the input and an AMD decoding of the output, respectively. (See Section 2.2 for a formal definition and constructions of AMD codes.) The circuit  $\widehat{C}$ , which gets input from  $\mathsf{Enc}$  and produces output for  $\mathsf{Dec}$ , is obtained by applying Theorem 1.1 to the circuit C' obtained from C by applying an AMD decoder to its input and an AMD encoder to its output. See Theorem 3.8 for a formal statement of the result we get by applying this construction to Theorem 1.1.

Theorem 1.1 does not provide any security guarantees for circuits over small fields. In particular, it cannot be used to protect boolean circuits. To handle general fields, we need to rely on a small, tamper-proof output decoder. Moreover, unlike the previous construction, here we only guarantee the *correctness* of the output(unless an error is detected) and do not provide any guarantees regarding the secrecy of the input in the presence of additive attacks. Below we define the stronger notion of correctness, which does not require a tamper-proof input encoder. (As before, the input can be protected by an input encoder via the use of AMD codes.) This feature will be useful when applying a composition-based approach for constructing AMD circuits in this setting.

**Definition 1.2** (Additive-attack correctness with decoder). Let  $\mathbb{F}$  be a finite field and let  $f : \mathbb{F}^n \to \mathbb{F}^k$ . We say that a pair of circuits  $(\widehat{C}, D)$  are an  $\epsilon$ -correct implementation of f with a decoder if the following holds:

- Completeness. For all  $\mathbf{x} \in \mathbb{F}^n$ , we have  $\Pr[D(\widehat{C}(\mathbf{x})) = (0, f(\mathbf{x}))] = 1$ .

- Additive-attack correctness. For any circuit  $\widetilde{C}$  obtained by subjecting  $\widehat{C}$  to an additive attack there exists  $\mathbf{a}^{\mathsf{in}} \in \mathbb{F}^n$  such that for all  $\mathbf{x} \in \mathbb{F}^n$

$$\Pr\left[D(\widetilde{C}(\mathbf{x})) \notin \mathsf{ERR} \cup \{(0, f(\mathbf{x} + \mathbf{a}^{\mathsf{in}}))\}\right] \le \epsilon$$

where  $\mathsf{ERR} = \{(z', z) : z' \in \mathbb{F} \setminus \{0\}, z \in \mathbb{F}^k\}$  and the probability is taken over the internal randomness of  $\widetilde{C}$ .

Like in Definition 1.1, we say that  $(\widehat{C}, D)$  is an  $\epsilon$ -correct implementation of a (deterministic or randomized) circuit C if  $(\widehat{C}, D)$  is an  $\epsilon$ -correct implementation of the function f computed by C.

In Section 4.2 we prove the following theorem.

**Theorem 1.2** (see Theorem 4.5). For any field  $\mathbb{F}$ , positive integer  $\sigma$  and arithmetic circuit  $C : \mathbb{F}^n \to \mathbb{F}^k$ there exist  $(\widehat{C}, D)$  that form an  $\epsilon$ -correct implementation of C with a decoder, where  $\epsilon = 2^{-\sigma} \cdot |C|$ ,  $|\widehat{C}| = |C| \cdot poly(\sigma)$ , and  $|D| = k \cdot poly(\sigma)$ .

Notice the differences between Theorems 1.1 and 1.2 above. Theorem 1.1 guarantees security for arithmetic circuits over large fields while Theorem 1.2 achieves the weaker notion of additive-attack correctness, which allows information to leak via the error flag, but without requiring the underlying field to be large. In particular, Theorem 1.2 can be used over the binary field.

Finally, in Appendix A we present an alternative construction based on a *Multiprover Interactive Proof* (MIP) systems. The parameters that can be obtained from known MIP systems are summarized by the following theorem.

**Theorem 1.3** (see Theorem A.2). For any positive integer  $\sigma$  and for any circuit descriptor F describing a circuit  $C : \{0,1\}^n \to \{0,1\}^k$  there exists a  $2^{-\sigma}$ -correct implementation  $(\widehat{C}, D)$  of C such that  $|\widehat{C}| = (\sigma + |C| \cdot |F|) \cdot polylog(\sigma, |C|, |F|)$  and  $|D| = (n + k + |F|) \cdot \sigma \cdot polylog(|C|, |F|)$ .

The advantage of the above construction over the previous one is that, for succinctly described circuits (see Definition A.1), the multiplicative overhead to the circuit size is only polylogarithmic in the security parameter  $\sigma$ . On the downside, the construction of Theorem 1.3 requires the decoder D to grow with the description size of C, thus making it meaningful only for circuits that have a succinct description. Moreover, D needs to grow linearly with the input size of C. Finally, this approach does not produce a construction with full additive-attack security, but only additive-attack correctness.

#### 1.2.2 Multiparty computation via AMD circuits

The notion of AMD circuits is motivated by the following application to secure multiparty computation (MPC). Our goal is to construct MPC protocols that are secure against active adversaries, starting from those which are secure only against passive adversaries. Unlike the prevalent approach of modifying the protocol itself to directly handle any deviations of an active adversary, our approach is to use the protocol as it is, but apply it to a modified circuit. That is, given an MPC protocol, secure against passive adversaries, for a function f computed by a circuit C, we apply the same protocol to a modified circuit  $\hat{C}^{AMD}$ . The circuit  $\hat{C}^{AMD}$ , in addition to computing the function, is also responsible for handling any consequences resulting from the adversary's deviations from the protocol. The circuit  $\hat{C}^{AMD}$  will be essentially an additively secure version of the original circuit; we show that, for several simple MPC protocols from the literature that were only designed to provide security against passive adversaries, this approach suffices to handle general active adversaries. This is discussed in Section 5.

In the following we describe different applications of this methodology in the context of prior results (see summary in Table 1).

For simplicity we consider an MPC model where the adversary can abort the execution of the protocol, and do not attempt to provide guaranteed output delivery. The latter can be achieved when there is an honest majority and a broadcast channel is available [RB89].<sup>6</sup> We note, however, that protecting against active attacks is highly nontrivial even in this setting, and moreover the efficiency comparison with previous works takes this simpler model into account.

We begin by deriving a simple version of the feasibility result of [RB89], for MPC in the presence of an honest majority, from the passive-secure BGW protocol with n = 2t + 1 parties. Formally, we obtain the following theorem (see Section 5.7):

**Theorem 1.4** (see Corollary 5.4). For any n-party functionality f represented by an arithmetic circuit C over a sufficiently large  $\mathbb{F}$  there exists an n-party protocol  $\pi$  that  $\epsilon$ -securely computes f with abort in the presence of an honest majority for  $\epsilon = O(|C|/|\mathbb{F}|)$ . The protocol involves communication of  $O(n^2|C|)$  field elements.

Here and in the following, one can eliminate the dependence of the error on the field size by using an extension field. This results in a multiplicative overhead of at most  $\sigma$  for reducing the error to  $2^{-\sigma}$ (see Corollaries 5.5, 5.8, 5.9 and 5.11).

In Section 5.8 we obtain a more efficient variant which has a communication complexity of  $O(n|C| + n^2)$  field elements. This asymptotically matches the communication complexity of the best known passive-secure protocol from [DN07], and is obtained by applying our methodology to this protocol.

<sup>&</sup>lt;sup>6</sup>Our protocols can be modified to have this feature, whenever it is achievable, by using standard techniques; however, the details are beyond the scope of this work.

| $\mathbf{Adv}$ | Resilience                | Security    | Communication complexity                            | Model  | $\mathbf{Ref}$ |

|----------------|---------------------------|-------------|-----------------------------------------------------|--------|----------------|

| passive        | T  < n/2                  | perfect     | $O(n^2 C )$                                         | plain  | [BGW88]        |

| passive        | T  < n/2                  | perfect     | $O(n C  + n^2)$                                     | plain  | [DN07]         |

| passive        | T  < n                    | perfect     | $O(n^2 C )$ for boolean circuits                    | ОТ     | [GMW87]        |

| passive        | T  < n                    | perfect     | $O(n^2 C )$                                         | OLE    | [IPS09]        |

| active         | T  < n/2                  | statistical | $\operatorname{poly}(n) \cdot  C $                  | plain  | [RB89]         |

| active         | T  < n/2                  | statistical | $O(n C  + n^2 \log n \cdot d_C) + \text{poly}(n)$   | plain  | [BFO12]        |

| active         | T  < n/2                  | statistical | $O(n^2 C )$                                         | plain  | $\S{5.7}$      |

| active         | T  < n/2                  | statistical | $O(n C +n^2)$                                       | plain  | § <b>5.8</b>   |

| active         | T  < n                    | statistical | $O(n^2 C  + \log  \mathbb{F}  \cdot d_C)$           | OT+OLE | [IPS09]        |

| active         | $ T  < (1/2 - \epsilon)n$ | statistical | $O(\log n \cdot  C ) + \operatorname{poly}(n, d_C)$ | plain  | [DIK10]        |

| active         | T  < n                    | statistical | $O(n^2 C )$                                         | OLE    | $\S{5.9}$      |

| active         | $ T  < n 	ext{ or }$      | statistical | $O(n^2 C )$                                         | plain  | §5.10          |

|                | $T = \{ dealer \}$        |             |                                                     |        |                |

Table 1: Comparison of information-theoretic MPC protocols for arithmetic circuits. In the above, n is the number of parties,  $\epsilon$  is an arbitrary small positive constant, C is an arithmetic circuit over a finite field  $\mathbb{F}$ ,  $d_C$  is the multiplicative depth of C, and T is the set of parties corrupted by the adversary. Statistical security means that the protocol securely realizes C (with abort) with at most  $O(|C|/|\mathbb{F}|)$ simulation error. The communication complexity column counts the total number of field elements that are communicated between the parties (where in the plain model we assume only the availability of secure point-to-point channels). An OLE oracle (an arithmetic generalization of OT) receives  $a, b \in \mathbb{F}$ from one party and x from another, and returns ax + b to the latter. The results highlighted in boldface are new.

**Theorem 1.5** (see Corollary 5.7). For any n-party functionality f represented by an arithmetic circuit C over a sufficiently large  $\mathbb{F}$  there exists an n party protocol  $\pi$  with communication complexity of  $O(n|C| + n^2)$  field elements, where  $\pi \epsilon$ -securely computes f with abort in the presence of an honest majority for  $\epsilon = O(|C|/|\mathbb{F}|)$ .

This gives a simpler alternative to a recent protocol from [BFO12] and improves its complexity by eliminating a quadratic overhead for each layer of the circuit, as well as a large polynomial additive term. See Table 1.

Next, we tackle the task of secure multiparty computation in the presence of an active adversary without an honest majority. Unfortunately, this task is impossible to achieve for arbitrary circuits in the plain model. Thus, we are forced to use some kind of a hybrid model or have an honestly-executed inputindependent preprocessing phase which is done before the execution of the protocol. In Section 5.9 we present results for secure multiparty computation using an arithmetic generalization of the OT-hybrid model, called the OLE-hybrid model [NP06, IPS09] (where an oracle receives  $a, b \in \mathbb{F}$  from one party and x from another, and returns ax + b to the latter) and in Section 5.10 we present our results in the preprocessing model.

Concretely, in Section 5.9 we use an arithmetic version of the GMW protocol [GMW87, IPS09] and obtain an *n*-party protocol for securely computing any functionality (represented by an arithmetic circuit C), without requiring an honest majority, using  $O(n^2|C|)$  calls to the OLE oracle. This improves over the protocol of [IPS09] that inherently requires  $\Omega(\sigma)$  additional oracle calls for achieving  $2^{-\sigma}$ -security, regardless of the field or circuit size. Formally:

**Theorem 1.6** (see Theorem 5.7). For any n-party functionality f represented by an arithmetic circuit

C there exists a protocol  $\pi$  in the OLE-hybrid model that  $\epsilon$ -securely computes C with abort for  $\epsilon = O(|C|/|\mathbb{F}|)$ . Moreover,  $\pi$  invokes the OLE oracle  $O(|C|n^2)$  times.

Finally, in Section 5.10 we address the goal of secure multiparty computation in the preprocessing model. We present a protocol for securely computing an *n*-party functionality (again represented as an arithmetic circuit C) that utilizes a preprocessing phase which runs before the computation of f starts and does not depend on the inputs to f. This phase can be implemented using an additional party called the *dealer* that sends correlated randomness to the parties. We strengthen previous results in the preprocessing model [IPS09, BDOZ11, IKM<sup>+</sup>13], which assume the dealer to be honest, by providing security when either the dealer or any subset of the other parties may be corrupted (though not both). Formally:

**Theorem 1.7** (see Theorem 5.9). For any n-party functionality represented by an arithmetic circuit C over  $\mathbb{F}$ , there exists a protocol  $\pi$  that uses an additional dealer, such that  $\pi$  is an  $\epsilon$ -secure protocol for computing C with abort against an active adversary controlling either the dealer or any other parties, where  $\epsilon = O(|C|/|\mathbb{F}|)$ . The dealer in  $\pi$  only distributes correlated randomness to the other parties.

### 1.3 Overview of techniques

## 1.3.1 Additive-attack security

We first present our result for additive-attack security (see Section 3.2 for details) for a computation over a large field  $\mathbb{F}$ . Suppose we are given an arithmetic circuit C. In its secure version  $\hat{C}$ , every wire of C is paired with a wire that carries a "MAC tag." Each gate in C is replaced by a small gadget which computes the original gate's output as well as a MAC tag for it; further, this gadget accepts the MAC tags of the inputs to the original gate, and carries out a MAC verification computation. Note that this verification circuitry itself is open to additive attacks. Nevertheless, we can arrange that  $\hat{C}$  will produce a random output if the MAC tag verification fails for a wire anywhere in the computation.

We present more details below. In the following we identify the gate g with its result; the meaning will be clear from the context.

The basic construction. For a gate's output wire g, its MAC value will simply be  $g \cdot v^d$ , where v is a randomly generated element of the underlying field  $\mathbb{F}$  (fixed to the same value for all gates), and d is the degree of the wire g (as a polynomial in the input variables). This MAC has property that multiplications can be performed on the MAC value homomorphically to obtain a value that can correspond to a MAC value of the result of a multiplication. Updating the MAC for an addition and subtraction gate is implemented using a simple gadget. The consistency check is implemented as follows. We first compute the result of the original gate, g. Next, we compute the MAC value in two ways. The first way is by directly multiplying g to  $v^d$  (in turn computed from v). The second way is using the MAC values of the inputs (homomorphically for multiplication and via a simple gadget for the case of addition and subtraction). We then check that the values are equal: more precisely, in each gate we take the difference of these two values, and linearly combine them across all gates using random coefficients; the result – which is a random field element if any inconsistency was detected, and 0 otherwise – is added to the final outcome.

We show that any additive attack on  $\widehat{C}$  is either equivalent to an additive attack on the input wires and /or output wires only, or else, results in the output being random, up to a statistical distance of  $O(d/|\mathbb{F}|)$  from the uniform distribution. Note that if the field is large (i.e., is of size exponential in the security parameter) and if d is small (for e.g., polynomial), we obtain negligible error in security. The security of the construction requires that the underlying circuit C be such that for every gate in C, the joint values of its two inputs should be almost uniformly distributed over  $\mathbb{F} \times \mathbb{F}$ . This is ensured by first compiling C into an appropriately randomized circuit (see below). One problem with the above basic construction is that the security error grows with the degree of the circuit. Since the degree of a circuit can be exponential in its depth, this construction does not yield a full solution to our problem. However, we show that bootstrapping from this construction for low-degree circuits, we can indeed obtain a construction that is secure for all polynomial-sized circuits (see below).

The randomization process. As noted above, the basic construction relies on the inputs to each gate of the given circuit being uniformly random. We can enforce this as follows. Each wire a inside the circuit C will be replaced by two wires, carrying values  $a + r_1$  and  $a + r_2$ , where the masking values  $r_1$  and  $r_2$ are generated as random field elements (that are the same throughout the circuit). Next, we will replace each multiplication and addition gate with a gadget that will get as input  $(a + r_1, a + r_2, b + r_1, b + r_2)$ and output either  $(ab + r_1, ab + r_2)$ ,  $(a + b + r_1, a + b + r_2)$  or  $(a - b + r_1, a - b + r_2)$  respectively. These gadgets have the property that the inputs of every internal gate are completely random. To complete the modification of the circuit, two additional layers are added. First, a layer of addition gates is added to the input wires to carry out the encoding. Next, a layer of subtraction gates is added to the output wires to carry out the decoding. Note that the inputs to the gates in these additional layers do not have the randomness property we set out to ensure for every gate (since the inputs and outputs are not random). However, attacks on these addition and subtraction gates are equivalent to attacks on the actual input and output of the circuit itself, and this is permitted by Definition 1.1.

**From low-degree circuits to arbitrary circuits.** Observe that additive-attack security could be easily achieved if we were allowed to use tamper-proof gadgets to implement each gate. Then each gate can be replaced by a tamper-proof component that gets two inputs encoded using an AMD code and, after decoding them, computes an AMD encoding of the gate's result. In our final construction, we implement these gadgets using the above construction for low-degree circuits and obtain a construction for arbitrary circuits.

#### 1.3.2 Handling small fields

Our constructions for additive-attack security inherently fail when the underlying field is small, even if we were willing to tolerate a small constant error (see Section 3.2.4 for details). In this section, we present an alternative construction that achieves additive-attack *correctness* over small fields, with negligible error (see Section 4.2 for details). Recall that correctness prevents the attacker from causing the circuit to output a wrong value without being detected.

**Basic construction without a decoder.** Our final construction will achieve additive-attack correctness using a small tamper-proof output decoder. But first, we present a construction that does not use any decoders but allows (inevitably) both inputs and outputs to besubject to additive attacks (see Definition 4.1). This construction will have a constant error. Later we will show how to amplify the correctness (and also improve the efficiency) of this construction, and meet the requirements of Definition 1.2, by relying on a small tamper-proof output decoder.

The basic idea is that our new circuit would compute not only the output of the original circuit, but also a *proof* that the output is correct; at the end of the computation, this proof will be verified by another part of the circuit. We need a simple proof system that can be implemented in such a way that soundness holds even when the verifier as well as the prover could be under (additive) attack.<sup>7</sup> Our proof system follows in the pattern of the Hadamard PCP system of [ALM<sup>+</sup>92], which turns out to have the linearity properties suitable for our purposes. However, we cannot use this PCP system as it is, since the proof is exponentially large. We use an alternate compact representation of the proof that suffices *if* we can ensure that the prover indeed computes prescribed linear functions of a purported

<sup>&</sup>lt;sup>7</sup>Even if we allowed a small tamper-proof decoder (which we do not for this basic construction), it would not be feasible to house the verifier there, since the verifier would be at least as large as the original circuit itself; allowing such a large tamper-proof component trivializes the problem.

witness and the verifier's queries. This condition on the prover is enforced by a "matrix multiplication gadget" (see below). The verifier's computation is simple and results in an error flag to be set (to a non-zero value) with at least a constant probability, if the proof is not valid.

It remains to ensure that under additive attack, the prover is restricted to computing the correct linear functions (but possibly using an invalid witness). This is achieved using the following gadgets.

The multiplication gadgets. We sketch our  $\epsilon$ -correct implementation (without output decoder) of a matrix-by-vector multiplication. For this, first we construct a scalar-by-vector multiplication gadget.

The inputs to a scalar-by-vector multiplication gadget consist of a vector  $\mathbf{v}$  and a scalar x, the output is  $\mathbf{v}x$ . The main idea of this construction is to make the circuit compute  $\mathbf{z} = \mathbf{v}x$  and  $q' = (\mathbf{r} \cdot \mathbf{v})x$ where  $\mathbf{r}$  is a random vector. To verify that  $\mathbf{r} \cdot \mathbf{z} = q'$ , we compute  $f = \mathbf{r}\mathbf{z} - q'$  as an error flag. We show that any attack that does not correspond to an additive attack on the inputs and outputs of the scalar-by-vector multiplication gadget will cause the flag to be set randomly.

We next proceed to the matrix-by-vector multiplication gadget. The inputs to such a gadget are a matrix M and a vector  $\mathbf{x}$ , and the output is  $\mathbf{z} = M\mathbf{x}$ . We implement this gadget using the scalarby-vector multiplication gadget. The main idea is as follows: we treat the *columns* of M as vectors and multiply each column with the required coordinate of  $\mathbf{x}$  using the scalar-by-vector multiplication gadget. Afterwards, we sum up these intermediate values to obtain the output of the matrix-by-vector multiplication. Since any attack on the scalar-by-vector multiplication gadget is equivalent to an attack on its inputs and outputs and since the matrix-by-vector multiplication gadget only sums up the results of the scalar-by-vector multiplication gadget, it will be the case that any attack on the matrix-by-vector multiplication gadget is either equivalent to an attack on its inputs and outputs or it causes its error flag to become non-zero with constant probability.

**Theorem 1.8** (informal; see Lemma 4.2). For any finite field  $\mathbb{F}$ , the function  $f(M, \mathbf{v}) = M\mathbf{v}$  admits a 0.95-correct implementation  $\widehat{C}$ .

Using this gadget to implement the prover in the above outline, we obtain the following result.

**Theorem 1.9** (informal; see Theorem 4.1). Any circuit C over a finite field  $\mathbb{F}$  admits a 0.997-correct implementation without output decoder,  $\widehat{C}$ , where  $|\widehat{C}| = O(|C|^2)$ .

**Correctness amplification.** For small fields (in particular, the binary field), the above construction has a high error probability. A naive attempt at reducing the error to  $\epsilon^{\sigma}$  would be to repeat the  $\epsilon$ -correct construction  $\sigma$  times, and then use a (tamper-proof) decoder to check for consistency. However, it is possible that different instances will be operating on different inputs, and therefore no amplification will be achieved (see Section 4.2.1). This problem can be solved by asking each instance of the construction to output its input in addition to the result and then using a decoder to verify that all the inputs are consistent. However, in this case the complexity of the decoder will be polynomial in the input size. Keeping the tamper-proof decoder size virtually independent (up to logarithmic factors) of the input size is crucial for the efficiency improvement we discuss next. Thus, we use a family of (almost pairwise independent) hash functions such that the circuit will output a hash digest of its input instead of the actual input. Since input consistency is still verified, attacks that cause different instances of the construction to operate on different inputs will cause inconsistency in the hash digests, and the decoder will then set the error flag wire to be non-zero.

**Theorem 1.10** (informal; see Theorem 4.3). Any circuit  $C : \mathbb{F}^n \to \mathbb{F}^k$  admits a  $2^{-\sigma}$ -correct implementation  $(\widehat{C}, D)$  where  $|\widehat{C}| = |C|^2 \cdot poly(\sigma)$  and  $|D| = k \cdot poly(\sigma)$ .

From quadratic to linear overhead. The above construction has quadratic overhead in the circuit size, since we use parts from the PCP prover of [ALM<sup>+</sup>92]. In particular, similarly to [ALM<sup>+</sup>92], our construction will compute all possible multiplications of two intermediate wires inside the circuit. We

improve this using "bootstrapping", as follows. We go over the gates of C in topological order. For each input gate, we apply the above construction to the single-wire identity circuit, yielding an  $\epsilon$ -correct gadget, and a corresponding decoder. Then, for each subsequent gate g, we consider the small circuit C' consisting of the decoders corresponding to the two gates of upstream of g, along with g itself, and apply the above construction to C' to yield an  $\epsilon$ -correct gadget and a new decoder, and so on. These are wired together. Finally, the decoders corresponding to the output gates, taken together, are considered the decoder for the resulting  $\epsilon$ -correct implementation of C.

Since the substitution replaces a gate with a small gadget whose size is independent of C, the resulting circuit size grows linearly with that of |C|.

**Theorem 1.11** (informal; see Theorem 4.5). Any circuit  $C : \mathbb{F}^n \to \mathbb{F}^k$  admits a  $(2^{-\sigma} \cdot |C|)$ -correct implementation  $(\widehat{C}, D)$  where  $|\widehat{C}| = |C| \cdot poly(\sigma)$  and  $|D| = k \cdot poly(\sigma)$ .

#### 1.3.3 Secure multiparty computation

We review the main techniques used for applying AMD circuits towards secure computation in the presence of an active adversary, as discussed in Section 1.2.2. (see Section 5)

Protecting the computation of circuits. We start from a protocol  $\pi$  that evaluates a circuit C with security against *passive* adversaries. In Section 5 we prove, for several useful protocols  $\pi$ , that when  $\pi$  is executed in the presence of an *active* adversary,  $\pi$  actually computes a circuit  $\widetilde{C}$  that is the same as C up to some additive attack that is chosen by the adversary. Thus, by replacing the circuit C with an additive-attack secure implementation  $\widehat{C}$  of C we obtain that any active attack on the protocol corresponds to an additive attack on the inputs and outputs of C.

**Protecting the inputs and outputs.** To protect the inputs and outputs of C against additive attacks, we construct another circuit  $C^{AMD}$  from C so that  $C^{AMD}$  gets its inputs in some AMD code, decodes them, and then applies C. Finally,  $C^{AMD}$  encodes the outputs of C using an AMD code. In addition, if  $C^{AMD}$  gets inputs that are not valid AMD encodings due to an additive attack by the adversary,  $C^{AMD}$  sets a special output flag to be random. This will notify the honest parties that they should abort the computation since the results might have been corrupted by the adversary.

The final protocol. We construct an active-secure MPC protocol  $\pi'$  for C as follows. First, all the parties locally encode their inputs using an AMD code. Then they invoke  $\pi$  on an additive-attack secure implementation  $\hat{C}^{AMD}$  of  $C^{AMD}$ . Finally, the parties locally decode the outputs of  $C^{AMD}$  obtained from the execution of  $\pi$  and abort if the decoding fails or if the error flag is nonzero. The security of  $\pi'$  is argued as follows. Notice that by the properties of  $\pi$ , the adversary is limited to only performing additive attacks on  $\hat{C}^{AMD}$ . Since  $\hat{C}^{AMD}$  is additive-attack secure, these attacks are equivalent (up to small statistical distance) to additive attacks on the inputs and outputs of  $\hat{C}^{AMD}$  will be detected by the AMD code, causing the honest parties to abort.

Applications to existing semi-honest MPC protocols. While our approach can be possibly extended to include many other protocols, in Section 5 we demonstrate our approach by using variants of existing semi-honest MPC protocols. Namely a variant of the semi-honest BGW protocol [BGW88], an arithmetic version of the semi-honest GMW protocol in the OLE-hybrid model [GMW87, IPS09] and a simplified version of the semi-honest DN protocol [DN07]. Thus, we are able to obtain protocols that are secure against active adversaries that have asymptotically the same communication complexity and number of oracle calls as their semi-honest versions.

Applying our methodology to the semi-honest DN protocol we obtain an *n*-party protocol  $\pi$  for  $O(|C|/|\mathbb{F}|)$ -securely computing a circuit C over some field  $\mathbb{F}$  with abort in the presences of an honest majority whose communication complexity is  $O(n|C| + n^2)$  field elements. Similarly, applying our methodology arithmetic version of the semi-honest GMW protocol in the OLE hybrid model [GMW87,

IPS09] we obtain an *n*-party protocol  $\pi$  for  $O(|C|/|\mathbb{F}|)$ -securely computing a circuit C over some field  $\mathbb{F}$  in the OLE hybrid model that invokes the OLE oracle  $O(n^2|C|)$  times.

Next, replacing the OLE oracle in the above protocol with a random OLE oracle (while making the necessary modifications to the protocol) and then asking an additional party called the *dealer* to compute the outputs of the random OLE oracle for all the parties, we obtain a protocol for computing a circuit C that is remains  $O(|C|/|\mathbb{F}|)$ -secure even when the adversary is allowed to corrupt either the dealer or any subset of the other parties (but not both).

#### 1.4 Related work

Fault tolerant circuits. The goal of securing cryptographic hardware against active attacks has motivated different models for fault-tolerant circuits that mainly aim to protect the *secrecy* of the data stored inside the circuits. All prior works along this line somehow restrict the attacker so that some of the wires in the circuit are unaffected. This could be done by either restricting the number of attacked wires or by requiring that the attack fail with some probability. In our case, we eliminate this requirement by only considering the restricted class of additive attacks.

Gennaro et al. [GLM<sup>+</sup>04] and, more recently, Tauman-Kalai et al. [KKS11] considered tampering attacks that apply only to the *memory* but not to the circuit logic. The work of Liu and Lysyanskaya [LL12] considered the question of protecting circuits against leakage and tampering in the splitstate model, where the leakage and tampering functions are not allowed to operate on the entire circuit at once but only on different parts of it. Ishai et al. [IPSW06], as well Dachman-Soled and Tauman-Kalai [DK12, DSK14], considered a reactive setting where in each clock cycle, the circuit produces outputs as well as updates its internal state. In their model, no part of the circuit must be free from tampering, but the adversary is restricted to tampering with a *bounded* number of wires in each clock cycle. Finally, Faust et al. [FPV11] considered a variant in which the adversary can attack every wire in the circuit, but each attack fails with some constant probability.

Additive attacks. As noted above, the goal of protecting *information* against additive attacks was previously considered in [CDF<sup>+</sup>08], who introduced AMD codes as a means of detecting such attacks. One of the motivating applications of AMD codes was that of converting any (passive-secure) linear secret sharing scheme into a similar scheme that offers error-detection in the presence of active tampering with the shares. Our application of AMD circuits to MPC is conceptually similar: we use AMD circuits to convert passive-secure MPC protocols with a certain "linear" structure into similar MPC protocols that offer security against active corruptions.

A concurrent and independent work of Ikarashi et al. [IKHC14] also makes the observation that in some natural passive-secure MPC protocols, any active attack on the protocol corresponds to an additive attack on the underlying circuit. This is then used to immunize such protocols against active attacks. The main result of [IKHC14] is a protocol with the same asymptotic complexity as the protocol of Section 5.8, which offers active security in the presence of an honest majority with a communication complexity of  $O(n|C| + n^2)$  field elements.

The protocol of [IKHC14] is simpler, has better concrete complexity than our corresponding protocol, and slightly better security  $(O(1/|\mathbb{F}|) \text{ vs. } O(|C|/|\mathbb{F}|))$ . It relies on the fact that the additive attacks induced by active attacks on the passive-secure protocol from [DN07] (as well as the simpler BGW protocol [BGW88]) have a limited form: only outputs of multiplication gates and output gates are vulnerable to attacks, and the additive attack is consistent across all the wires connecting the output of a gate to the inputs of other gates. The protocol from [IKHC14] implicitly relies on a simple construction of AMD circuits that tolerate such restricted additive attacks. This construction does not protect against more general additive attacks. Protecting against general additive attacks seems necessary for securing other passive-secure protocols to which we apply our methodology, such as the semi-honest GMW protocol in the OLE hybrid model [GMW87, IPS09].

# 2 Preliminaries

## 2.1 Definitions

We begin by defining the notion of arithmetic circuits. We extend the standard notion of arithmetic circuits (Cf. [SY10]) by allowing randomness gates as well as gates the compute arbitrary functions.

**Definition 2.1** (Arithmetic circuit). Let  $\mathbb{F}$  be a finite field and let  $\mathcal{G}$  be a set of functions  $g_i : \mathbb{F}^{n_i} \to \mathbb{F}$ . An arithmetic circuit C over the gate set  $\mathcal{G}$  and a set of variables  $X = \{x_1, \dots, x_n\}$  is a directed acyclic graph whose vertices are called gates and whose edges are called wires. Every gate in C of in-degree 0 is either labeled by a variable from X and is referred to as an input gate or is labeled by the constant one and is referred to as one gate. All other gates are labeled by functions from  $\mathcal{G}$ . Every gate of out-degree 0 is called an output gate. We assume that the output gates are ordered. In some cases we also allow in-degree 0 gates labeled by rand and referred to as randomness gates. A circuit containing rand gates is called a randomized circuit and a circuit that does not contain rand gates is called a deterministic circuit.

Unless stated otherwise, we shall assume that  $\mathcal{G} = \{+, -, \times\}$ . Gates labeled by +, - and  $\times$  are called addition, subtraction or multiplication gates respectively. We assume that the in-degree of addition, subtraction and multiplication gates is 2.

We write  $C : \mathbb{F}^n \to \mathbb{F}^k$  to indicate that C is an arithmetic circuit over  $\mathbb{F}$  with n inputs and k outputs. We denote by |C| the number of gates in C. A one gate outputs the field element 1. Similarly, a randomness gate outputs a random element from  $\mathbb{F}$ . For an input  $\mathbf{x} \in \mathbb{F}^n$  we denote by  $C(\mathbf{x})$  the result of evaluation C on  $\mathbf{x}$  if C is deterministic and the resulting distribution if C is randomized. For a pair of circuits  $C_1 : \mathbb{F}^n \to \mathbb{F}^k$  and  $C_2 : \mathbb{F}^k \to \mathbb{F}^t$  we define the circuit  $C_2(C_1(\cdots))$  as the circuit obtained from connecting the outputs of  $C_1$  to the inputs of  $C_2$ .

The degree of each gate in C, as well as the degree of C are defined as follows.

**Definition 2.2** (Degree). We use  $\deg(g)$  to denote the degree of gates defined as follows. If g is an input or rand gate then  $\deg(g) = 1$ . If g is a one gate then  $\deg(g) = 0$ . If  $g = g_a + g_b$  or  $g = g_a - g_b$  then  $\deg(g) = \max(\deg(g_a), \deg(g_b))$ . Finally, if  $g = g_a \times g_b$  then  $\deg(g) = \deg(g_a) + \deg(g_b)$ . The degree of a circuit C, denoted by  $\deg(C)$ , is defined to be the maximal degree of all gates of C.

Attack model. Intuitively, an additive attack A on a deterministic or randomized circuit C changes the computation by "blindly" adding a constant field element to every wire in C as well as to the outputs of C. Let  $C : \mathbb{F}^n \to \mathbb{F}^k$  be a circuit. An *additive attack* A on C assigns an element of  $\mathbb{F}$  to each of its internal wires as well as to each of the C's outputs. We denote by  $A_{u,v}$  the attack A restricted to the wire (u, v). Similarly we denote by  $A_{out}$  the restriction of A to the outputs of C.

An additive attack A changes the computation performed by the circuit C as follows. For every wire (u, v) in C, the value  $A_{u,v}$  is added to the output of u before it enters the inputs of v. Similarly, the value  $A_{out}$  is added to the outputs of C. For a circuit  $C : \mathbb{F}^n \to \mathbb{F}^k$  and an additive attack A, we denote by  $\widetilde{C} \leftarrow A(C)$  the circuit resulting from the additive attack A on C.

**Notation.** Let  $\mathbb{F}$  be a finite field, we use  $\mathbb{F}^*$  to denote both  $\mathbb{F} \setminus \{0\}$  and the multiplicative group of  $\mathbb{F}$ . The meaning will be clear from the context. Let  $\mathbf{u}, \mathbf{v} \in \mathbb{F}^n$ . Denote by  $v_i$  the *i*'th coordinate of  $\mathbf{v}$ . Denote by  $\mathbf{v} \cdot \mathbf{u}$  the inner product over  $\mathbb{F}$  of  $\mathbf{v}$  and  $\mathbf{u}$ . When appears inside a circuit construction we define  $\mathbf{v} \cdot \mathbf{u}$  to be the circuit computing  $\sum_{i=1}^n v_i \cdot u_i$  by multiplying the coordinates of  $\mathbf{v}$  and  $\mathbf{u}$  using *n* multiplication gates and then summing up the result using addition gates.

Notice that in the case of addition gates, any attack on their input wires has an equivalent attack on their output wires. Thus, we can assume without loss of generality that only the input wires of multiplication and output gates are attacked since the attack on inputs of addition gates can be pulled "downstream" through them until the inputs of multiplication or output gates. **Lemma 2.1.** Let C be a randomized arithmetic circuit and let A be an additive attack. Then there exists an additive attack A' that only attacks the inputs of multiplication and outputs of output gates of C such that for all x it holds that

$$\widetilde{C}(x) \equiv \widetilde{C}'(x)$$

where  $\widetilde{C} \leftarrow A(C)$  and  $\widetilde{C}' \leftarrow A'(C)$ .

**Distributions.** Denote by  $U_n$  the uniform distribution over  $\mathbb{F}^n$  and denote by  $U^*$  the uniform distribution over  $\mathbb{F}^*$ . If two distributions  $D_1$  and  $D_2$  are the same we denote that by  $D_1 \equiv D_2$ . We will rely on the following standard claims.

Claim 2.1. Let  $\Delta_1, \Delta_2, \Delta_3$  be distributions such that  $SD(\Delta_1, \Delta_2) = \epsilon$  and  $SD(\Delta_2, \Delta_3) = \epsilon'$ . Then,  $SD(\Delta_1, \Delta_3) \leq \epsilon + \epsilon'$ .

**Claim 2.2.** Let  $\Delta_1, \Delta_2$  be two distributions such that  $SD(\Delta_1, \Delta_2) \leq \epsilon$ . Then, for any function f it holds that  $SD(f(\Delta_1), f(\Delta_2)) \leq \epsilon$ .

## 2.2 AMD codes

In this section we study the goal of encoding information in a way that will allow us to pass it from one part of the circuit to the other without the adversary being able to alter the information in an undetectable way.

Intuitively, we would like to find a pair of arithmetic circuits (Enc, Dec) over some field  $\mathbb{F}$  with the following two properties First, Dec can always recover x from the output of Enc invoked on input x. Second, any additive attack mounted on the outputs of Enc will be detected with some non-zero probability. Finally, we require that the size of (Enc, Dec) does not depend on the size of  $\mathbb{F}$ . Formally,

**Definition 2.3.** An  $(n, k, \epsilon)$ -AMD code is a pair of circuits (Enc, Dec) where Enc :  $\mathbb{F}^n \to \mathbb{F}^k$  is randomized and Dec :  $\mathbb{F}^k \to \mathbb{F}^{n+1}$  is deterministic such that the following properties hold:

• Perfect completeness. For all  $\mathbf{x} \in \mathbb{F}^n$ ,

$$\Pr[\mathsf{Dec}(\mathsf{Enc}(\mathbf{x})) = (0, \mathbf{x})] = 1.$$

• Additive robustness. For any  $\mathbf{a} \in \mathbb{F}^k$ ,  $\mathbf{a} \neq 0$ , and for any  $\mathbf{x} \in \mathbb{F}^n$  it holds that

$$\Pr[\mathsf{Dec}(\mathsf{Enc}(\mathbf{x}) + \mathbf{a}) \notin \mathsf{ERR}] \le \epsilon.$$

We also define the notion of private  $(n, k, \epsilon)$ -AMD code that has the same completeness and security requirements as well as additional privacy requirement that for any  $\mathbf{a} \in \mathbb{F}^k$ ,  $\mathbf{a} \neq 0$ ,  $y \in \mathbb{F}^* \times \mathbb{F}^k$ , and for any  $\mathbf{x}, \mathbf{x}' \in \mathbb{F}^n$  it holds that

$\Pr\left[\mathsf{Dec}(\mathsf{Enc}(\mathbf{x}) + \mathbf{a}) = y \,|\, \mathsf{Dec}(\mathsf{Enc}(\mathbf{x}) + \mathbf{a}) \in \mathsf{ERR}\right] = \Pr\left[\mathsf{Dec}(\mathsf{Enc}(\mathbf{x}') + \mathbf{a}) = y \,|\, \mathsf{Dec}(\mathsf{Enc}(\mathbf{x}') + \mathbf{a}) \in \mathsf{ERR}\right].$

Notice that private AMD codes could be easily constructed from AMD codes by requiring the decoder to output random values in the case where a corruption is detected. Formally, consider Construction 2.1 below.

**Construction 2.1.** Let (Enc, Dec) be a  $(n, k, \epsilon)$ -AMD code. Consider the circuits (Enc', Dec') that are defined as follows.

- The circuit Enc' on input x outputs Enc(x).

- The circuit Dec' on input x performs the following.

- 1. Compute  $(b, \mathbf{y}) \leftarrow \mathsf{Dec}(\mathbf{x})$ .

- 2. Output  $(0, \mathbf{y}) + b\mathbf{r}$  where  $\mathbf{r}$  is generated uniformly from  $\mathbb{F}^{n+1}$ .

The following theorem can be easily verified.

**Theorem 2.1.** For any pair of circuits (Enc, Dec) that are an  $(n, k, \epsilon)$ -AMD code, the pair of circuits (Enc', Dec') defined in Construction 2.1 are a private  $(n, k, \epsilon)$ -AMD code.

Asymptotically optimal constructions of such codes have been introduced by [DKRS06] and by [CDF<sup>+</sup>08].

**Theorem 2.2** (Implicit in [CDF<sup>+</sup>08] Corollary 1). For any positive integers  $n, \sigma$  and field  $\mathbb{F}$  there exists a pair of circuits (Enc, Dec) over  $\mathbb{F}$  that are an  $(n, O(n+\sigma), \frac{1}{|\mathbb{F}|^{\sigma}})$ -AMD code. Moreover, the size of Enc and Dec is  $O(n+\sigma)$ .

In fact,  $[CDF^+08]$  consider a slightly weaker definition of AMD codes where is it guaranteed that  $Pr[Dec(Enc(\mathbf{x}) + \mathbf{a}) \notin ERR \cup \{(0, \mathbf{x})\}] \leq \epsilon$ . However, their construction actually has the stronger security property of Definition 2.3. Combining Theorem 2.2 with the construction of private AMD codes outlined above we obtain the following:

**Corollary 2.1.** For any positive integers  $n, \sigma$  there exists a pair of circuits (Enc, Dec) such that for any finite field  $\mathbb{F}$  it holds that (Enc, Dec) are a private  $(n, O(n + \sigma), \frac{1}{|\mathbb{F}|^{\sigma}})$ -AMD code. Moreover, the size of Enc and Dec is  $O(n + \sigma)$ .

# 3 AMD circuits over large finite fields

#### 3.1 Simplifying the circuit model

Our constructions below assume that  $\mathcal{G}$  is composed out of addition, subtraction and multiplication gates and do not consider circuit that contain one gates. It is possible to apply our constructions on a circuit C over a field  $\mathbb{F}$  containing one gates as follows.

**Construction 3.1** (Removing constants). Let C be a circuit containing one gates, construct the  $\epsilon$ -secure implementation  $\hat{C}$  of C as follows.

- 1. Replace the one gates in C with an input gate g and obtain the circuit C' that outputs the output of C if the output of g is 1 and a random value otherwise (this can be implemented by generating a random value r and outputting z + (gr r) where z is the output of C).

- 2. Notice that C' does not contain one gates but assumes that the constant 1 is given in the input gate g. Let  $\widehat{C'}$  we an  $\epsilon$ -secure implementation of C'.

- 3. Construct the circuit  $\widehat{C}$  obtained from  $\widehat{C'}$  by connecting a one gate to g.

The following lemma immediately follows from the fact that any additive attack on  $\widehat{C}$  is equivalent to an additive attack on the inputs and outputs of C' and is therefore equivalent to an additive attack on the inputs and outputs of C and on the **one** gate used in C. Notice that any attack on the on **one** is caught by C' causing the outputs of  $\widehat{C}$  to become random.

**Lemma 3.1.** For any circuit C containing one gates, the circuit  $\widehat{C}$  constructed in Construction 3.1 is an  $(\epsilon + \frac{1}{\|\mathbb{F}\|})$ -secure implementation of C.

**Remark 3.1.** Our constructions for additive-attack correctness below also do not deal with circuits containing one gates. However, it is possible to apply them on circuits that contain one gates using an analog of Construction 3.1 and Lemma 3.1.

Unless stated otherwise, in the sequel we will assume that our constructions will be only applied on deterministic circuits that *do not* contain randomness gates. It is possible to apply our constructions on a circuit C over a field  $\mathbb{F}$  containing randomness gates as follows.

**Construction 3.2** (Removing randomness gates). Let C be a randomized circuit, construct the  $\epsilon$ -secure implementation  $\widehat{C}$  of C as follows.

- 1. First, replace every randomness gate  $g_i$  in C with an input gate  $g'_i$  and obtain the circuit C'. Let  $\widehat{C'}$  be an  $\epsilon$ -secure implementation of C'.

- 2. Construct the circuit  $\widehat{C}$  obtained from  $\widehat{C'}$  by replacing every  $g'_i$  created in the previous step with a randomness gate.

The following lemma immediately follows from the fact that any additive attack on  $\hat{C}$  is equivalent to an additive attack on the inputs and outputs of C as well as on the randomness gates of C. Notice that any additive attack on the randomness gates of C does not effect the distribution of the obtained randomness.

**Lemma 3.2.** For any randomized circuit C, the circuit  $\widehat{C}$  constructed in Construction 3.2 is an  $\epsilon$ -secure implementation of C.

**Remark 3.2.** Our constructions for additive-attack correctness below also do not deal with circuits containing randomness gates. However, it is possible to apply them on circuits that contain randomness gates using an analog of Construction 3.2 and Lemma 3.2.

The security of guarantee of Theorem 1.1 directly relates to the size of the field  $\mathbb{F}$  over which the circuit is defined. It is possible to amplify the security of Theorem 1.1 by computing C over a suitable extension field  $\mathbb{H}$  of  $\mathbb{F}$ . Since the adversary is allowed to attack the inputs of a secure implementation of C, we cannot apply our constructions on C over  $\mathbb{H}$  directly. Instead, we must modify C to a circuit C' over  $\mathbb{H}$  that checks that the inputs to C are indeed elements of  $\mathbb{F}$  and then apply our constructions on C'. Formally, consider the following theorem.

**Theorem 3.1** (Amplifying additive-attack security). For any circuit  $C : \mathbb{F}^n \to \mathbb{F}^k$  and  $\sigma > 0$  there exists a randomized circuit  $\widehat{C} : \mathbb{H}^n \to \mathbb{H}^k$  over some extension field  $\mathbb{H}$  of  $\mathbb{F}$  such that  $\widehat{C}$  is a  $O(2^{-\sigma})$ -secure implementation of C.

**Proof.** Let  $\mathbb{H}$  be an extension field of  $\mathbb{F}$  such that  $|\mathbb{H}| \geq (|C| + n \log |\mathbb{F}|) \cdot 2^{\sigma}$ . Notice that for any field element  $x \in \mathbb{H}$  such that  $x \neq 0$  it holds that  $x^{|\mathbb{F}|-1} = 1$  if and only if  $x \in \mathbb{F}$ . Define a circuit  $C'(\mathbf{x}) = C(\mathbf{x}) + \left(\sum_{i=1}^{n} s_i \cdot B\left(x_i^{|\mathbb{F}|-1}\right)\right) \cdot \mathbf{r}$  over  $\mathbb{H}$  where  $s_1, \dots, s_n$  are random field elements generated using randomness gates inside C',  $\mathbf{r}$  is a random vector over  $\mathbb{H}^k$  generated using random gates inside C' and B(x) = x(1-x) is a polynomial that vanishes only on 0 and 1. Notice that if the input does not belong to the field  $\mathbb{F}$  then the output of C' is uniformly random and that  $C'(\mathbf{x}) = C(\mathbf{x})$  for every input  $\mathbf{x} \in \mathbb{F}^n$ . In addition, by construction we have that  $|C'| = O(|C| + n \log |\mathbb{F}|)$ . Let  $\widehat{C}$  be an  $O(|C'|/|\mathbb{H}|)$ -secure implementation of C'. Notice that since  $|\mathbb{H}| \geq (|C| + n \log |\mathbb{F}|) \cdot 2^{\sigma}$  it holds that  $\widehat{C}$  is an  $O(2^{-\sigma})$ -secure implementation of C as well.

#### 3.2 Protecting low-degree circuits over large finite fields

In this section we construct  $\epsilon$ -secure implementations for low-degree arithmetic circuits over large finite fields. The main idea behind the construction is as follows. We would like to ensure that any additive attack on the circuit will have one of two consequences: it will either cause the circuit to output a random output for all inputs, or it will be equivalent to a set of wire corruptions on the inputs and the outputs of the circuit. To do so, we will encode the values in the circuit and compute over encoded values. The special property of the encoding is that every additive attack on the encoded values will cause the encoding to become invalid. We first present a simpler construction whose security holds when the wire values satisfy some local randomness property (Section 3.2.1). Later, we show how to eliminate this assumption by applying a general transformation to the circuit (Section 3.2.2). Finally, we combine the two together into a secure construction for low-degree circuits and arbitrary inputs (Section 3.2.3). We begin by presenting the security notion for specific input distributions.

**Definition 3.1** (Additive-attack security with respect to a distribution). Let  $\mathbb{F}$  be a finite field,  $C : \mathbb{F}^n \to \mathbb{F}^k$  an arithmetic circuit, and I a distribution over  $\mathbb{F}^n$ . We say that a circuit  $\widehat{C} : \mathbb{F}^n \to \mathbb{F}^k$  is an  $\epsilon$ -secure implementation of C with respect to I if the following holds:

• Completeness. For all  $\mathbf{x} \in \mathbb{F}^n$ ,

$$\widehat{C}(\mathbf{x}) \equiv C(\mathbf{x}).$$

• Additive-attack security with respect to *I*. For any additive attack *A*, there exists  $\mathbf{a}^{in} \in \mathbb{F}^n$  and a distribution  $\mathcal{A}^{out}$  over  $\mathbb{F}^k$  such that

$$SD\left(\widetilde{C}(I), C(I + \mathbf{a}^{\mathsf{in}}) + \mathcal{A}^{\mathsf{out}}\right) \leq \epsilon$$

where  $\widetilde{C} \leftarrow A(\widehat{C})$ .

#### 3.2.1 Additive-attack security for locally-random distributions

We now present a secure construction for constant degree circuits and specific input distributions. Similarly to the approach of [BDOZ11, DPSZ12] for secure computation with preprocessing (and somewhat similarly to the MAC-based quantum MPC protocol of [BCG<sup>+</sup>06]), our construction is based on a simple homomorphic MAC. However, in contrast to [BDOZ11, DPSZ12], we do not rely on any preprocessing phase to correctly produce MACed data, used to protect the circuit evaluation. Instead, our construction remains secure even when the sub-circuits computing and verifying the MAC tags are also subject to an additive attacks.

The main idea is to add for every wire in the circuit another wire carrying its MAC value. When two wires enter a gate the two MAC values corresponding to them will enter a special circuit that will produce the expected MAC value of the gate's result. Afterwards, the result of the gate and the corresponding MAC value are checked. The MAC used will have the property that if an input to a gate is attacked then the MAC value produced separately for this gate will not verify with the gate's result. As soon as this situation is detected a special abort flag will become non-zero causing the entire circuit to output a random value.

The construction will guarantee security as defined in Definition 3.1 with  $\epsilon = O\left(\frac{d}{|\mathbb{F}|}\right)$ , where d is the degree of the circuit it is applied on, under two assumptions.

- 1. The inputs of each gate are sufficiently random. In Section 3.2.2 we present a transformation that will randomize the inputs of each gate in the circuit.

- 2. The input to the circuit is taken from a specific input distribution. In Section 3.2.3 we present a construction for arbitrary inputs.

Since the security of the construction depends on the degree of the circuit, the construction is only useful for low-degree circuits. We start by defining what it means for inputs of each gate to be random and not to depend on the input to the circuit. Formally,

Figure 1: MAC computation for multiplication gates ( · denotes field multiplication).

**Definition 3.2.** Let  $\mathbb{F}$  be a finite field,  $C : \mathbb{F}^n \to \mathbb{F}^k$  a randomized arithmetic circuit, and I a distribution over  $\mathbb{F}^n$ . We say that C is locally  $\epsilon$ -random with respect to I if for any  $(y, z) \in \mathbb{F}^2$ , and any pair of gates  $(g_1, g_2)$  whose outputs are the inputs to the same gate in C, it holds that the probability over  $\mathbf{x} \leftarrow I$  and the internal randomness of C that the outputs of  $(g_1, g_2)$  in  $C(\mathbf{x})$  are equal to (y, z) is at most  $\epsilon$ .

We now describe a construction that takes as input an  $\epsilon$ -random circuit with respect to some class of input distributions and transforms it to a secure circuit with respect to the same class of distributions. The idea is as follows. For gate  $g_c$  with inputs  $g_a$  and  $g_b$ , the circuit will compute a MAC for  $g_c$  in two ways. The first way is by computing the gate's result and obtaining the MAC directly from the result. This MAC value is denoted in the construction below by  $f'_c$ . The second way is by homomorphically combining the input MACs  $f'_a$  and  $f'_b$  into a MAC for  $g_c$ . This MAC value is denoted below by  $g'_c$ . Finally, the circuit will verify that  $f'_c = g'_c$ . The guarantee of the MAC is that every additive attack is either harmless and will not affect the result, or it will be the case that  $f'_c \neq g'_c$  with high probability. In the latter case, a special wire inside the circuit will become non-zero and will cause the entire circuit to output a random value. Intuitively, this guarantee is achieved by utilizing the fact that addition and multiplication do not commute.

See Figure 3.2.1 for the MAC for multiplication gates. Formally, consider Construction 3.3 below.

**Construction 3.3.** Let  $C : \mathbb{F}^n \to \mathbb{F}^k$  be a circuit. Let  $g_i$ ,  $1 \le i \le |C|$ , denote the gates of C in some topological order. Define a circuit  $\widehat{C}$  that on input **x** performs the following:

- 1. Compute  $\mathbf{z} = C(\mathbf{x})$ .

- 2. Generate a random field element  $v \in \mathbb{F}$ .

- 3. For  $i = 1, ..., \deg(C)$  compute  $p_i = v^i$  using multiplication gates.

- 4. For any gate  $g_i$  of degree  $d_i$ , compute the value  $f'_i = g_i \cdot p_{d_i}$ .

- 5. For each non-input gate  $g_c$ , c = n + 1, ..., |C|, let  $g_a$  and  $g_b$  be its inputs and let  $d_a$  and  $d_b$  be their degrees. Compute the value  $g'_c$  as follows:

- If  $g_c$  is a multiplication gate, let  $g'_c = f'_a \cdot f'_b$ .

- If  $g_c$  is an addition gate: (1) if  $d_a > d_b$  let  $h'_c = p_{d_a-d_b} \cdot f'_b$  and  $g'_c = f'_a + h'_c$ , (2) if  $d_a < d_b$  let  $h'_c = p_{d_b-d_a} \cdot f'_a$  and  $g'_c = h'_c + f'_b$ , and (3) if  $d_a = d_b$  let  $g'_c = f'_a + f'_b$ .