## A Tutorial on the Implementation of Block Ciphers: Software and Hardware Applications

Howard M. Heys

Memorial University of Newfoundland, St. John's, Canada email: hheys@mun.ca

Dec. 10, 2020

## Abstract

In this article, we discuss basic strategies that can be used to implement block ciphers in both software and hardware environments. As models for discussion, we use substitutionpermutation networks which form the basis for many practical block cipher structures. For software implementation, we discuss approaches such as table lookups and bit-slicing, while for hardware implementation, we examine a broad range of architectures from high speed structures like pipelining, to compact structures based on serialization. To illustrate different implementation concepts, we present example data associated with specific methods and discuss sample designs that can be employed to realize different implementation strategies. We expect that the article will be of particular interest to researchers, scientists, and engineers that are new to the field of cryptographic implementation.

# **Terminology and Notation**

| Abbreviation | Definition                              |

|--------------|-----------------------------------------|

| SPN          | substitution-permutation network        |

| IoT          | Internet of Things                      |

| AES          | Advanced Encryption Standard            |

| ECB          | electronic codebook mode                |

| CBC          | cipher block chaining mode              |

| CTR          | counter mode                            |

| CMOS         | complementary metal-oxide semiconductor |

| ASIC         | application-specific integrated circuit |

| FPGA         | field-programmable gate array           |

Table 1: Abbreviations Used in Article

| В                                                                                                         | plaintext/ciphertext block size                                                                              |  |  |  |

|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                                                           |                                                                                                              |  |  |  |

|                                                                                                           | (also, size of cipher state)                                                                                 |  |  |  |

| $\kappa$                                                                                                  | number of cipher key bits                                                                                    |  |  |  |

|                                                                                                           | (also, size of key state)                                                                                    |  |  |  |

| R                                                                                                         | number of rounds                                                                                             |  |  |  |

| n                                                                                                         | S-box size (number of input/output bits)                                                                     |  |  |  |

| $P = [p_{B-1}p_1p_0]$<br>$C = [c_{B-1}c_1c_0]$                                                            | plaintext block of $B$ bits                                                                                  |  |  |  |

| $C = [c_{B-1}c_1c_0]$                                                                                     | ciphertext block of $B$ bits                                                                                 |  |  |  |

| $K = [k_{\kappa-1}k_1k_0]$                                                                                | $\kappa$ -bit cipher key                                                                                     |  |  |  |

| $D = [d_{B-1}d_1d_0]$                                                                                     | B-bit cipher state                                                                                           |  |  |  |

| $D^* = [d^*_{B-1}d^*_1d^*_0]$ $X = [x_{B-1}x_1x_0]$                                                       | B-bit next cipher state                                                                                      |  |  |  |

| $X = [x_{B-1}x_1x_0]$                                                                                     | B-bit cipher state at input to substitution layer                                                            |  |  |  |

|                                                                                                           | and output of key mixing layer                                                                               |  |  |  |

| $Y = [y_{B-1}y_1y_0]$                                                                                     | B-bit cipher state at output of substitution layer                                                           |  |  |  |

|                                                                                                           | and input to permutation layer                                                                               |  |  |  |

| $Z = [z_{B-1}z_1z_0]$                                                                                     | B-bit cipher state at output of permutation layer                                                            |  |  |  |

|                                                                                                           | and input to key mixing layer                                                                                |  |  |  |

| $RK_r = [rk_{r,B-1}rk_{r,1}rk_{r,0}]$                                                                     | B-bit round key of round $r$                                                                                 |  |  |  |

|                                                                                                           | $\kappa$ -bit key state                                                                                      |  |  |  |

| $P^{\dagger} = [P_{B-1}^{\dagger} P_{1}^{\dagger} P_{0}^{\dagger}]^{T}$                                   | bit-slice plaintext structure:                                                                               |  |  |  |

|                                                                                                           | $B \times B$ matrix of bits consisting of B rows of                                                          |  |  |  |

|                                                                                                           | <i>B</i> -bit plaintext blocks, $P_i^{\dagger}, i \in \{0, 1,, B-1\}$                                        |  |  |  |

| $\frac{p_{i,j}^{\dagger}}{C^{\dagger} = [C_{p_1}^{\dagger} \dots C_{q_1}^{\dagger} C_{q_1}^{\dagger}]^T}$ | element at row i, column j of $P^{\dagger}$ , $i, j \in \{0, 1,, B-1\}$                                      |  |  |  |

| $C^{\dagger} = [C_{B-1}^{\dagger} C_{1}^{\dagger} C_{0}^{\dagger}]^{T}$                                   | bit-slice ciphertext structure:                                                                              |  |  |  |

|                                                                                                           | $B \times B$ matrix of bits consisting of B rows of                                                          |  |  |  |

|                                                                                                           | B-bit ciphertext blocks, $C_i^{\dagger}, i \in \{0, 1,, B-1\}$                                               |  |  |  |

| $D^{\dagger} = [D_{B-1}^{\dagger}D_{1}^{\dagger}D_{0}^{\dagger}]^{T}$                                     | bit-slice cipher state:                                                                                      |  |  |  |

|                                                                                                           | $B \times B$ matrix of bits consisting of B columns of                                                       |  |  |  |

|                                                                                                           | <i>B</i> -bit cipher states, $D_i^{\dagger}, i \in \{0, 1,, B-1\}$                                           |  |  |  |

| $d_{i,i}^{\dagger}$                                                                                       | element at row <i>i</i> , column <i>j</i> of $D^{\dagger}$ , <i>i</i> , <i>j</i> $\in$ {0, 1,, <i>B</i> - 1} |  |  |  |

Table 2: Notation Used in Article

# Contents

| 1        | Intr | roduction to Block Ciphers 9                     |

|----------|------|--------------------------------------------------|

|          | 1.1  | Target Implementation Environments    9          |

|          | 1.2  | Basic Cipher Principles 11                       |

|          | 1.3  | Substitution Permutation Networks                |

|          |      | 1.3.1 16-bit SPN 12                              |

|          |      | 1.3.2 64-bit SPN 17                              |

|          | 1.4  | Modes of Operation                               |

|          |      | 1.4.1Electronic CodeBook Mode19                  |

|          |      | 1.4.2 Cipher Block Chaining Mode                 |

|          |      | 1.4.3 Counter Mode                               |

|          | 1.5  | General Implementation Structures                |

|          | 1.6  | Summary                                          |

| <b>2</b> | Soft | tware Implementation 25                          |

|          | 2.1  | Structure of Encryption                          |

|          | 2.2  | Structure of Decryption                          |

|          | 2.3  | Direct Implementation of an SPN                  |

|          |      | 2.3.1 Key Mixing Layer Implementation            |

|          |      | 2.3.2 Substitution Layer Implementation          |

|          |      | 2.3.3 Permutation Layer Implementation           |

|          | 2.4  | Table Lookup Implementations    29               |

|          |      | 2.4.1 Permutation in a Table                     |

|          |      | 2.4.2 Combined Substitution/Permutation Table    |

|          | 2.5  | Time/Memory Tradeoffs of Lookup Tables    33     |

|          | 2.6  | Bit-slice Implementations                        |

|          |      | 2.6.1 Bit-slicing the S-box                      |

|          |      | 2.6.2 Restructuring the Data for Bit-Slicing     |

|          |      | 2.6.3 Bit-slicing the Permutation and Key Mixing |

|          |      | 2.6.4 Example of Bit-Slicing                     |

|          |      | 2.6.5 Other Structures for Bit-slicing           |

|          | 2.7  | Software Implementation of Cipher Modes          |

|          | 2.8  | Summary 47                                       |

### CONTENTS

| 3            | Har   | rdware Implementation 4                         | 9         |

|--------------|-------|-------------------------------------------------|-----------|

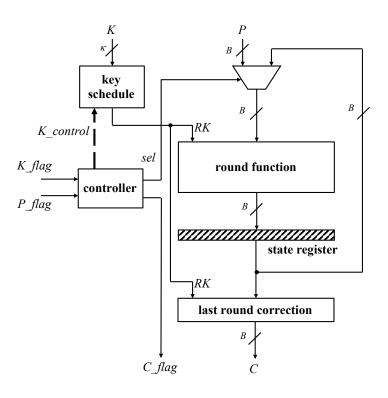

|              | 3.1   | Iterative Design                                | 0         |

|              |       | 3.1.1 Basic Iterative Architecture              | 0         |

|              |       | 3.1.2 Round Function Hardware                   | <b>52</b> |

|              |       | 3.1.3 Loop Unrolling                            | 3         |

|              | 3.2   | Parallelization - A High Speed Implementation 5 | 55        |

|              | 3.3   | Pipelining - A High Speed Implementation        | 6         |

|              |       | 3.3.1 Description of Pipeline Architecture      | 6         |

|              |       | 3.3.2 Selecting Hardware for a Pipeline Stage   | 8         |

|              |       | 3.3.3 Timing Issues for Pipeline Designs 5      | 8         |

|              |       | 3.3.4 Example of Pipelining 5                   | 9         |

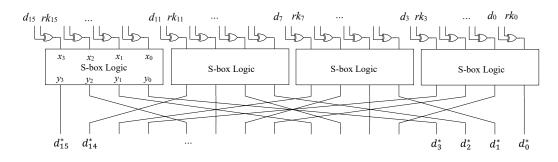

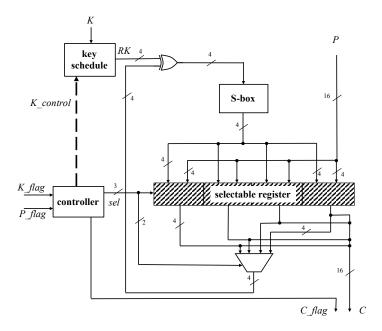

|              | 3.4   | Serial Design - A Compact Implementation        | 60        |

|              |       | 3.4.1 The Concept of Serialization              | 51        |

|              |       | 3.4.2 A Sample Design                           | 51        |

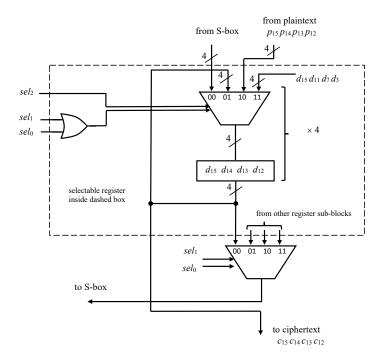

|              |       | 3.4.3 Selectable Register                       | 53        |

|              | 3.5   | Hardware Implementation of Decryption           | 5         |

|              | 3.6   | Hardware Implementation of Cipher Modes         | 6         |

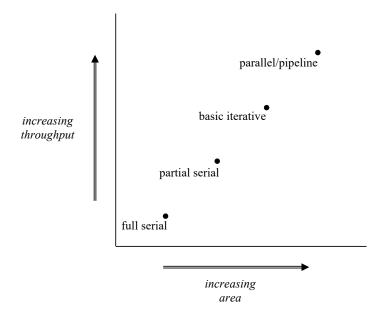

|              | 3.7   | Tradeoffs Between Architectures                 | 6         |

|              | 3.8   | Summary                                         | 9         |

| 4            | Cor   | nclusion 7                                      | 1         |

| R            | efere | nces 7                                          | 3         |

| $\mathbf{A}$ | ppen  | dix: Key Scheduling 7                           | 7         |

8

## Chapter 1

## **Introduction to Block Ciphers**

Block ciphers are the workhorse of security applications. Using a symmetric key approach, block cipher algorithms encrypt a block of plaintext bits (typically, 64 or 128 bits) to produce an equally-sized block of ciphertext bits. These algorithms can be found in a broad range of application environments and it is almost certainly true that the best known block cipher, the Advanced Encryption Standard (AES) [1][2], is the most applied cipher in the world today.

## **1.1 Target Implementation Environments**

Implementations of block ciphers can be divided into two broad categories: software and hardware. Software implementations make use of the instructions available on general purpose processors, while hardware implementations focus on designs at the level of logic gates and registers. Of course, within these two categories, there are many sub-categories dependent on the processor characteristics for software (eg. instruction set, word size, memory availability, etc.) and the technology for hardware (eg. CMOS application-specific integrated circuits (ASICs) and field-programmable gate arrays (FPGAs)). Implementation choices are invariably influenced by the objectives of the application and the features of the targeted environment. This results in the consideration of factors such as speed and resource constraints including chip area, system memory, and device power or energy limitations.

As examples of the diversity of target environments, consider that block ciphers could be implemented for the following 3 sample scenarios:

- 1. a general purpose computer using a processor with a word size of 64-bits (that is, instructions use 64-bit operands and data is stored as 64-bit words),

- 2. a device targeted to an application for the Internet of Things (IoT), making use of either (a) a small processor (eg. a microcontroller) or (b) custom dedicated hardware of limited area, and

- 3. a high speed communications gateway targeted to service many high speed data connections.

Now, consider briefly for these different environments, the resources needed and the influences of those resource requirements on the implementation of the block cipher. For the 64bit general purpose computer, there is likely to be lots of memory and a comprehensive instruction set with a large word size for operands and in such implementations probably speed of encryption (or throughput) is of most interest. In contrast, the implementation targeted to the IoT device would be fundamentally concerned with the constrained resources such as memory and word size for a small processor or circuit area and power/energy limitations for a hardware implementation. Hence, for the IoT device, it is necessary to consider *lightweight cryptography* [3] and, for the applications to which such a device is targeted, speed of the encryption process is usually not an important consideration. Lastly, for the high speed communications gateway, speed of encryption is so important that it is often desirable to utilize custom designed hardware implementations that give the ability to process many different connections at high speeds.

Clearly, there are a breadth of potential applications and, as a result, there are many different considerations when implementing ciphers. In many scenarios, different types of implementations could be employed within the same application. For example, an IoT device might interact with a software application on a general purpose computer. In some circumstances, specially-targeted ciphers are proposed that are intended specifically for one or more these environments. For example, many recently proposed block cipher algorithms are considered lightweight, targeted specifically to implementation on constrained devices. In such cipher proposals, implementation approaches are often discussed by the cipher proponents. In practice, however, it is often desirable to have a cipher be applied to many different environments, which may vary dramatically in the nature of their requirements. This is case, for example, for AES, which can be found in all manner of targeted environments from high speed software to compact hardware architectures. The near-ubiquity of AES has lead to processors with special instructions to facilitate encryption speedup [4] and the development of specialized hardware structures suitable for the specific components defined for AES (for example, see [5]).

In this article, we choose to focus our discussions on the general principles that can be applied to the implementations of ciphers on many different platforms. We do not get into details which are targeted to one particular cipher and, instead, describe approaches that can generally be applied to the majority of proposed block ciphers. The main objective of the article then is not to provide a detailed description of the implementation for a particular cipher or ciphers, but instead present the principles that form the foundation for understanding how ciphers can be implemented. This is accomplished by using illustrative examples and sample designs of cipher implementations. This article is a starting point for the cryptographic engineer wanting to have an understanding of the general structures and methods found in implementations before the engineer delves more deeply into the possible architectures suitable to their cipher of interest. To this end, we present a basic form of block cipher, referred to as the *substitution-permutation network (SPN)*, which we then use as the basis of our discussion of implementation approaches.

## **1.2** Basic Cipher Principles

We first discuss some of the fundamental principles with which all block ciphers are designed.<sup>1</sup> Block ciphers encrypt a block of plaintext, P, of size B bits by applying a key-dependent transformation to produce an B-bit block of ciphertext, C. The key, K, is defined to be  $\kappa$ bits in size, giving a key space with a total of  $2^{\kappa}$  possible keys. Block ciphers fall into the category of *symmetric key* cryptography. Such ciphers have the same key applied for both encryption and decryption.

Typically,  $B \ge 64$ . Compact, lightweight ciphers, such as the PRESENT block cipher [6], targeted to constrained systems environments (such as some devices for IoT), which require implementation efficiency but which can typically accommodate lower security levels, have smaller block sizes of 64 bits, while ciphers like AES used for a broad range of applications, are usually expected to have higher security levels and large block sizes (eg. 128 bits). Block ciphers with very small block sizes (such as 32 bits) would not acceptable for any context, because a small block size may make a dictionary attack practical, where the attacker is able to acquire some known plaintext and corresponding ciphertext and build a table of plaintext-ciphertext mappings for a system with a given secret key.

The key size,  $\kappa$ , must be large enough to ensure that a brute force or exhaustive key search attack is not possible. In such an attack, knowledge of a small number of plaintext blocks and corresponding ciphertext blocks could be utilized by the attacker who can encrypt the plaintext with all possible keys to determine which key results in the corresponding known ciphertext. Using only a modest number of plaintext/ciphertext pairs, the key found can be confirmed to be the correct one. To prevent this, generally,  $\kappa \geq 80$ , with the lower bound being suitable for low security lightweight applications, while values like  $\kappa = 128$  or 256 would be used for higher security general applications. For example, the PRESENT cipher is defined to operate with 80 or 128 bits of key and AES allows keys of 128, 192, and 256 bits in size.

Cryptography has been around for millenia, but in the 1940s, Claude Shannon was the first to propose practical structures for the modern ciphers in use today. In [7], he describes the concept of a product cipher, where a cipher can be constructed as a composition of functions, with the functions consisting of simple cryptographic operations. Hence, he proposed constructing a block cipher by iterating over a number of rounds of operations, which, while not in themselves secure, have properties which provide security after many repetitions of the operations. Specifically, he proposed the concepts of *confusion* and *diffusion* as necessary properties of a block cipher which should be realized by the cipher's operations. Confusion is defined as the property creating a complex mathematical relationship between input bits and output bits; diffusion reflects that any grouping of a small number of input bits has an influence across all output bits.

<sup>&</sup>lt;sup>1</sup>Note that we use the word "design" in two contexts in this article. We sometimes refer to cipher design when referring to the functionality and security of the cipher algorithm, and, in this case, the design is often described using mathematical and algorithmic notation. Alternatively, we shall also refer to design when discussing of the implementation of the cipher and, in this case, we are implying the software functions or hardware structures that are used to realize the cipher.

## **1.3** Substitution Permutation Networks

A substitution-permutation network (referred as an SP network, or simply an SPN) is a wellknown structure for realizing the characteristics of Shannon's product cipher. Numerous cipher proposals over the years have used the concepts found in SPNs. For example, the PRESENT cipher is an SPN and, most notably, AES has a structure that is very similar to an SPN.

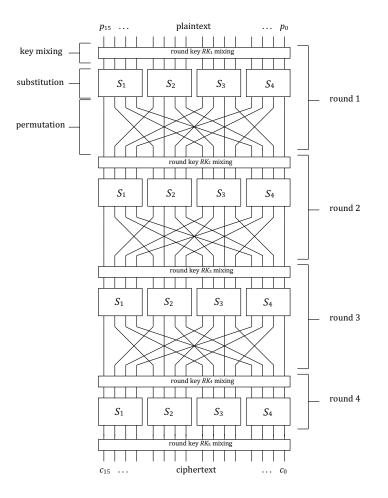

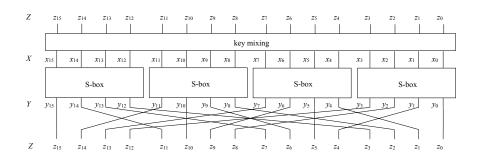

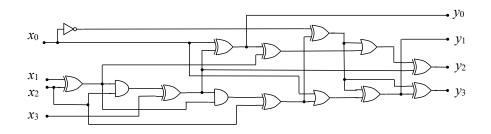

#### 1.3.1 16-bit SPN

Let's consider a simple realization of an SPN in the form of the trivial, toy cipher structure shown in Figure 1.1. This cipher is impractically small with only a 16-bit block size, but is useful in understanding the concepts of an SPN and forms a good foundation for discussing many of the implementation methods that we present in this article. The SPN illustrated in Figure 1.1 consists of 4 rounds. Each round (with the exception of the last round) consists of 3 cryptographic operations or layers: (1) round key mixing (or round key addition), (2) substitution, and (3) permutation. The last round has the permutation layer replaced by another key mixing layer. The block size is 16 bits and the plaintext input at the top of the diagram is labelled  $P = [p_{15}p_{14}...p_0]$ . At the output of the 4th round, the ciphertext is presented as  $C = [c_{15}c_{14}...c_0]$ , at the bottom of the diagram.<sup>2</sup> Data blocks flow through the cipher and are acted upon by each layer. We shall refer to the 16-bit data block within the cipher as the *cipher state*. In this article, we shall generally use D to represent the state.<sup>3</sup>

To decrypt, the process is reversed. Essentially, at the bottom of the diagram, the ciphertext is provided as input to the decryption process, data flows up the structure (backwards through all the layers) and comes out as plaintext output, at the top of the diagram. We discuss decryption in more detail, later in this section.

#### **Encryption Process**

The structure illustrated presents the path that data follows during the encryption process. To produce the bits mixed with the state bits during the key mixing operation, a key scheduling algorithm generates round keys. (The key scheduling process is not illustrated in the figure.) For round r, the 16-bit round key is labelled as  $RK_r$ . Usually, these bits are produced by simple operations on the original cipher key bits, parameterized by some unique information related to the round number. We discuss the key schedule in detail in the Appendix. During the key mixing operation, the round key, which is 16 bits in size, is XORed on a bit-by-bit basis with the cipher state. The key mixing operations in PRESENT and AES are similar, except in those cases, the round keys sizes are the same as the corresponding block sizes and the XOR is across the block of 64 bits or 128 bits, respectively.

Following the key mixing, the state is conceptually broken up into 4 sub-blocks, each of 4 bits (that is, one nibble). In the substitution layer, each 4-bit sub-block is processed with

$<sup>^{2}</sup>$ We present the discussion of our ciphers using language that presumes the cipher is used in electronic codebook mode, one of several modes discussed in Section 1.4. For other cipher modes, it is perhaps more appropriate to refer to the forward (reverse) process, rather than the encryption (decryption) process.

<sup>&</sup>lt;sup>3</sup>Note that, in subsequent sections, we shall also use notation in some contexts where X, Y, and Z represent the state.

Figure 1.1: 16-bit SPN (4 Rounds)

a substitution box or *S*-box. A 4-bit S-box takes a 4-bit input and maps it to a 4-bit output as shown in Figure 1.2. The 4-bit S-box operation can be thought of as a table lookup (and can be implemented as such) where the table consists of  $2^4$  nibbles. The input is used as an index into the table and the output is selected from the position pointed to by the index. An S-box is a fixed mapping (i.e., it is not key dependent) and an example of a 4-bit S-box is shown in Table 1.1. This is the S-box found in the PRESENT cipher [6]. PRESENT is an SPN and, as with many lightweight ciphers, it uses a small S-box mapping. In contrast, AES uses an 8-bit S-box which is represented by a table of  $2^8$  8-bit values, indexed by the 8-bit input. In the substitution layer, it is conceivable that all S-boxes are defined to be different mappings (this was the case, for example, with the Data Encryption Standard [8]), but it is more typical for ciphers to use only one mapping for all S-boxes. This is the case for the PRESENT cipher (with one 4-bit S-box defined) and AES (with one 8-bit S-box

Figure 1.2: S-box Notation

| input  | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|--------|---|---|---|---|---|---|---|---|

| output | С | 5 | 6 | В | 9 | 0 | Α | D |

| input  | 8 | 9 | Α | В | С | D | Е | F |

|        |   |   |   |   |   |   |   |   |

Table 1.1: PRESENT 4-bit S-box Mapping (All values in hexadecimal.)

defined). In our discussion, we shall implicitly assume that all S-boxes in a cipher use the same mapping.

The properties of the S-box are critical to the proper operation and security of the cipher. In order to be able to map, for a given key, a plaintext to a unique ciphertext (and vice versa), the S-box must be bijective (that is, one-to-one). Bijectivity guarantees that each output bit of the S-box is balanced, meaning that for half of the input values, the output bit is "0" and half "1". Another important property that the mapping must possess is that the output bits are a nonlinear functions of the inputs. This is necessary to provide Shannon's confusion property and prevent successful linear cryptanalysis of the cipher [9]. Many other properties of the S-box are also desirable to prevent other cryptanalytic attacks, such as differential cryptanalysis [10]. The study of the construction of S-boxes to ensure certain cryptographic properties is an extensive field of research and a discussion of this topic is beyond the scope of this article.

The last operation of a round in the SPN is the permutation. The permutation is simply a transposition of the bit positions of the state, shown as wirings in Figure 1.1. This can be easily described in a table as shown by the example in Table 1.2. Let  $D = [d_{15}d_{14}...d_0]$ represent the state bits at the input to the permutation and  $D^* = [d_{15}^*d_{14}^*...d_0^*]$  represent the state bits at the output of the permutation. Hence, the bits from the leftmost S-box,  $S_1$ , entering the permutation result in the following assignments to the state bits at the output of the permutation:  $d_{15}^* \leftarrow d_{15}$ ,  $d_{11}^* \leftarrow d_{14}$ ,  $d_7^* \leftarrow d_{13}$ , and  $d_3^* \leftarrow d_{12}$ . This means that the output bits of the leftmost S-box,  $S_1$ , are connected by the permutation to the inputs of all 4 S-boxes in the next round. This property of the permutation and the fact that any one bit input to an S-box has an effect on all S-box output bits ensures that isolated effects in the leftmost 4 bits will be spread across the block in the next round and can affect all

| input  | 15 | 14 | 13 | 12  | 11 | 10 | 9 | 8 |

|--------|----|----|----|-----|----|----|---|---|

| output | 15 | 11 | 7  | 3   | 14 | 10 | 6 | 2 |

| input  | 7  | 6  | 5  | 4   | 3  | 2  | 1 | 0 |

| output | 13 | 0  | -  | - 1 | 10 | 0  | 4 | 0 |

Table 1.2: 16-bit Permutation (Bit 15 is leftmost bit.)

| Operation    | Input | Output | Comment                         |

|--------------|-------|--------|---------------------------------|

| Key Mixing   | DEBE  | B0C7   | Round 1 with $RK_1 = 6E79$      |

| Substitution | B0C7  | 8C4D   |                                 |

| Permutation  | 8C4D  | D701   |                                 |

| Key Mixing   | D701  | B7DC   | Round 2 with $RK_2 = 60DD$      |

| Substitution | B7DC  | 8D74   |                                 |

| Permutation  | 8D74  | C726   |                                 |

| Key Mixing   | C726  | 49E5   | Round 3 with $RK_3 = 8EC3$      |

| Substitution | 49E5  | 9E10   |                                 |

| Permutation  | 9E10  | C44A   |                                 |

| Key Mixing   | C4AA  | 1354   | Round 4 with $RK_4 = D71E$      |

| Substitution | 1354  | 5B09   |                                 |

| Key Mixing   | 5B09  | 2AA3   | Replace permutation with        |

|              |       |        | key mixing using $RK_5 = 71$ AA |

Table 1.3: 16-bit SPN Encryption Example (All values in hexadecimal.)

output bits of the next round. This is exactly the diffusion concept of Shannon's product cipher. For AES, the diffusion in the cipher is not accomplished by a permutation, but by a linear transformation which is comprised of the ShiftRows and MixColumns operations [2]. However, a permutation is a very specific form of a linear transformation, so in a sense, AES belongs to a generalized class of SPNs, which replaces the permutation with the more general concept of a linear transformation. Many other block ciphers also fall into this class.

Note in Figure 1.1 that the last round of encryption uses a key mixing operation in place of the permutation. If there was no key mixing after the last layer of S-boxes, there would be no cryptographic purpose for the last round S-boxes, since it would a trivial matter for an attacker to go backwards through the S-boxes, knowing their output. Effectively, the last layer of S-boxes could therefore be stripped off the cipher by an attacker with virtually no effort. A layer of key mixing after the last layer of S-boxes ensures that the outputs of the S-boxes are unknown, as they are obscured to an attacker by the unknown round key bits.

In Table 1.3, we present example state values associated with encryption using the 16bit SPN with the S-box of Table 1.1 and the permutation of Table 1.2. All data in the example is in hexadecimal format. The input plaintext, P, is DEBE<sub>16</sub>, and we use the round keys presented in the table, which are derived in the example of Table A.1 discussed in the Appendix. The resulting ciphertext, C, is 2AA3<sub>16</sub>.

| input  | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|--------|---|---|---|---|---|---|---|---|

| output | 5 | E | F | 8 | C | 1 | 2 | D |

| input  | 8 | 9 | Α | В | С | D | Е | F |

| output | В | 4 | 6 | 3 | 0 | 7 | 9 | Α |

Table 1.4: 4-bit Inverse S-box (All values in hexadecimal.)

#### **Decryption Process**

As mentioned, decryption involves going backwards through the network. This has 3 implications:

- 1. decryption uses the inverse of the components used for encryption,

- 2. the round keys used in decryption are the same as for encryption but applied in reverse order, and

- 3. with the adjustment of round key bit positions, decryption can be viewed as similar in structure to encryption.

Consider the 3 layers and their inverses. The XOR function of the key mixing is trivially reversed. Assume input state bit d is XORed with round key bit rk to produce a new state bit,  $d^*$ :  $d^* = d \oplus rk$ . The inverse of this operation produces output d given input  $d^*$  and this is trivially possible using the operation  $d = d^* \oplus rk$  based on the properties of XOR. The inverse S-box is easily derived by reversing the roles of input and output. Hence, for an S-box which maps input 0011<sub>2</sub> (3<sub>16</sub>) to output 1011<sub>2</sub> (B<sub>16</sub>), the inverse S-box maps input 1011<sub>2</sub> (B<sub>16</sub>) to output 0011<sub>2</sub> (3<sub>16</sub>). Hence, the S-box defined by Table 1.1 has the inverse S-box given in Table 1.4. Finally, the permutation is obviously easily invertible by reversing the wiring associated with the permutation. For example, input bit 4 leads to output bit 1, implying for the inverse permutation, input bit 1 leads to output bit 4. For the permutation of Table 1.2, the inverse permutation is identical to the permutation.

It is clear that, since decryption is equivalent to processing from the bottom of Figure 1.1 to the top, the round key  $RK_5$  must be applied first and round key  $RK_1$  last in decryption. Hence, it is necessary to run through the complete key schedule to derive the last round key before decrypting any ciphertext. In suitable environments where the required memory is available, the round keys can be stored during this process and then used later during decryption. However, for many environments, particularly for hardware implementations, it is not possible to store all round keys and instead the key schedule will need to be run in reverse from the last round key, concurrently with the processing in the decryption datapath.

Lastly, decryption can be restructured to look like encryption, which could be important to some implementations where similar structures between encryption and decryption might lead to efficient, easily understood designs. Going backwards through Figure 1.1, we can see that we process a key mixing of  $RK_5$  and (inverse) substitution first, then follow with a key mixing of  $RK_4$  after which the (inverse) permutation is applied. But if we take the bits of  $RK_4$  and reorder them based on the inverse permutation, we can perform the inverse permutation before the key mixing and follow the inverse permutation with a key mixing

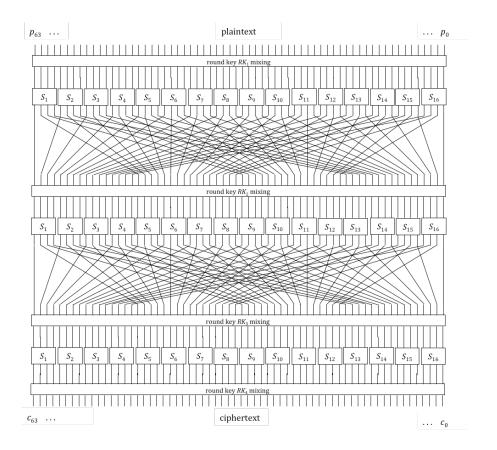

Figure 1.3: 64-bit SPN (3 rounds)

with the reordered  $RK_4$ . Similarly, we can reorder  $RK_3$  and  $RK_2$  and apply them after the inverse permutation in the decryption process. In doing this, we have the same order of cryptographic layers in the decryption process as in the encryption process.

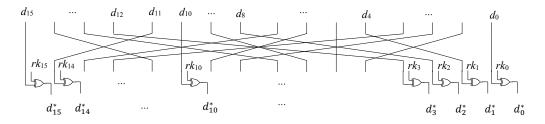

#### 1.3.2 64-bit SPN

In the previous section, we presented and discussed the components in a toy 16-bit cipher. While the block size of this cipher is not at all practical, the components described, including the 4-bit S-box are realistic and ciphers with larger block sizes exist which are similar in structure. In this section, we present a realistically-sized 64-bit SPN block cipher. This cipher structure is, in fact, equivalent the structure of the PRESENT cipher [6]. PRESENT is an important, foundational cipher in the area of lightweight cryptography and is a recommended ISO standard [11].

The architecture of the 64-bit SPN consisting of 3 rounds is given in Figure 1.3. The figure illustrates the placement of the key mixing layer, but does not show the key scheduling

| input  | 63 | 62 | 61 | 60 | 59 | 58 | 57 | 56 |

|--------|----|----|----|----|----|----|----|----|

| output | 63 | 47 | 31 | 15 | 62 | 46 | 30 | 14 |

| input  | 55 | 54 | 53 | 52 | 51 | 50 | 49 | 48 |

| output | 61 | 45 | 29 | 13 | 60 | 44 | 28 | 12 |

| input  | 47 | 46 | 45 | 44 | 43 | 42 | 41 | 40 |

| output | 59 | 43 | 27 | 11 | 58 | 42 | 26 | 10 |

| input  | 39 | 38 | 37 | 36 | 35 | 34 | 33 | 32 |

| output | 57 | 41 | 25 | 9  | 56 | 40 | 24 | 8  |

| input  | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 |

| output | 55 | 39 | 23 | 7  | 54 | 38 | 22 | 6  |

| input  | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| output | 53 | 37 | 21 | 5  | 52 | 36 | 20 | 4  |

| input  | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  |

| output | 51 | 35 | 19 | 3  | 50 | 34 | 18 | 2  |

| input  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

| output | 49 | 33 | 17 | 1  | 48 | 32 | 16 | 0  |

Table 1.5: 64-bit Permutation (Bit 63 is leftmost bit.)

algorithm which generates the round keys to mix. Although the block size and potential key size for this cipher are practical, such a cipher with only 3 rounds would not be secure and would be susceptible to many cryptanalytic attacks. Decryption would be accomplished by effectively going backwards (bottom to top) through the structure shown. The PRESENT cipher, while similar in structure, consists of 31 rounds, chosen to ensure security for an 80-bit or 128-bit key.

For PRESENT, one mapping is used for all S-boxes and it is given by the mapping presented in Table 1.1. The permutation illustrated in the figure is summarized in Table 1.5. The key mixing uses bit-by-bit XOR, which in this case is done across the 64-bit state and makes use of a 64-bit round key generated using a key schedule applied to the full cipher key (which is either 80-bits or 128-bits for PRESENT).

## **1.4** Modes of Operation

In order to efficiently and securely use a block cipher, one must use the cipher in an appropriate mode of operation. There are many different modes that have been defined with different objectives in mind. Fundamentally a mode must be secure and must provide the characteristics of significance for the targeted application. The mode employed can have an important impact on the implementation selected. Alternatively, the desired implementation structure (based on the application requirements) can impact the selected mode. We briefly describe three well-known modes [12], but note that many more are proposed and applied in practice.

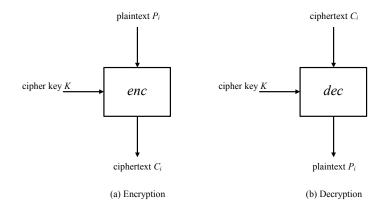

Figure 1.4: Electronic CodeBook Mode

#### 1.4.1 Electronic CodeBook Mode

Electronic CodeBook (ECB) mode is likely the natural mode one thinks about for block ciphers. To encrypt the *i*-th block of plaintext, one applies the block to the input of the block cipher and, using the cipher key as a parameter, produces the *i*-th block of ciphertext at the output. This is illustrated in Figure 1.4. Note that Figures 1.1 and 1.3 have their inputs and outputs labelled with the presumption that they are used in ECB mode. That is, the input to the block cipher operation is the plaintext and the output is the ciphertext. As we shall see, this is not the case for other modes.

In practice, it is not generally advisable to use ECB for the encryption of large amounts of data, because it is not considered to be semantically secure (that is, it is possible to determine some information about the plaintext by observing ciphertext). Consider, for example, that a known plaintext block  $P_i$  is encrypted in ECB mode using a particular key to produce the known observed ciphertext block  $C_i$ . If we later observe a second ciphertext  $C_j$  (produced using the same key), such that  $C_j = C_i$ , we can then determine that the plaintext  $P_j$  used to produce  $C_j$  must be the same as  $P_i$ , that is,  $P_j = P_i$ . This is a potentially significant source of leakage of plaintext information based on observing the ciphertext and having knowledge of some plaintext/ciphertext pairs and could be a serious problem if large amounts of data, such as might be the case when protecting keys by encrypting them so that they can be transferred confidentially between parties.

Note that, generally, our discussion in this article is presented using language which implies the use of ECB mode. However, the implementation methods can be clearly translated into other modes as appropriate and we do provide some discussion on the suitability of implementations for different modes.

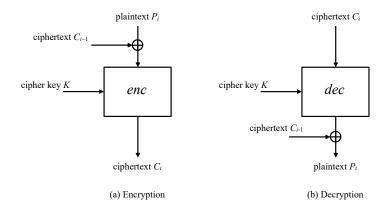

Figure 1.5: Cipher Block Chaining Mode

#### 1.4.2 Cipher Block Chaining Mode

Cipher Block Chaining (CBC) is a mode of operation which can be effectively used to encrypt large amounts of data using a block cipher without the semantic security issues associated with ECB mode. Encryption and decryption using CBC mode is illustrated in Figure 1.5. To encrypt the *i*-th block in a sequence of many plaintext blocks, CBC mode would XOR the plaintext block,  $P_i$ , with the ciphertext produced for the previous block,  $C_{i-1}$ . The resulting block is then fed to the input of the block cipher (operating as an encryption process) with the resulting output considered to be the ciphertext  $C_i$ . The first plaintext block,  $P_1$ , uses an *initialization vector* (IV) as  $C_0$ , since no ciphertext block yet exists. Decryption in CBC mode takes the ciphertext,  $C_i$ , as input to the block cipher (operating as a decryption process), from which the plaintext  $P_i$  is derived following XOR of the result with the previous ciphertext block,  $C_{i-1}$ .

The chaining aspect ensures that the encryption of a block is dependent on the encryption results from previous ciphertexts, thereby preventing the problem of ECB mode where two identical plaintext blocks result in identical ciphertext blocks. In typical encryption applications, the IV should be a *nonce*, which is a variable only assigned any value once. Hence, for CBC mode, different sessions will start the chain using IVs which should be unique to avoid semantic security issues with the first block. However, in many applications it is not necessary to keep IVs secret. CBC can be used as a general method to encrypt large amounts of data, consisting of many plaintext blocks and can be found applied in many contexts.

#### 1.4.3 Counter Mode

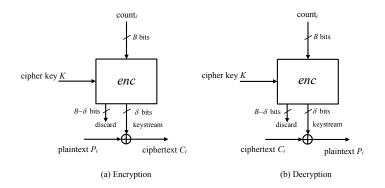

Counter (CTR) mode is another block cipher mode of operation suitable for encrypting a large amount of plaintext data. In CTR mode, the block cipher is configured to operate as a stream cipher, which produces ciphertext bits by XORing plaintext bits with *keystream* bits. In CTR mode, illustrated in Figure 1.6, the block cipher takes as input a B-bit counter

Figure 1.6: Counter Mode

value, labelled as "count<sub>i</sub>", with the resulting output of the block cipher used as keystream to be XORed on a bitwise basis with data from the plaintext block. Although the block cipher can be used to produce a full block of B bits of keystream, in general terms,  $\delta$  bits can be used as keystream (with the other  $B - \delta$  bits being discarded) to be XORed with a  $\delta$ -bit block of plaintext,  $P_i$ , where  $\delta \leq B$ .

The counter values, count<sub>i</sub>, can be straightforwardly incremented for every block cipher operation or can be a simple, predictable sequence of unique values. For decryption, the operation is identical to encryption, except the roles of plaintext and ciphertext reverse. The counter values at both sides of the communication must be synchronized in order for ciphertext  $C_i$  to decrypt properly to plaintext  $P_i$ . Decryption is possible in this way because of the properties of XOR: for bits C (ciphertext), P (plaintext), and Q (keystream),

$$C = P \oplus Q \Rightarrow P = C \oplus Q.$$

The initial count value should be unique for the first block of a session, but generally need not be kept secret. Note that both encryption and decryption use the encryption process of the block cipher to produce the keystream. Hence, an implementation of CTR mode does not require an implementation of the block cipher decryption process, which may result in significant memory and area savings in software and hardware implementations, respectively.

## **1.5** General Implementation Structures

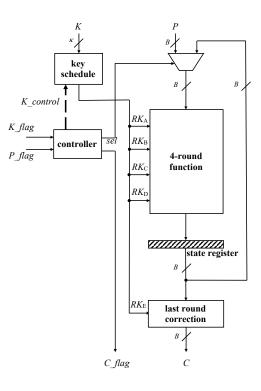

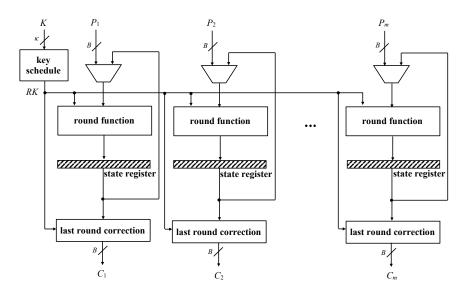

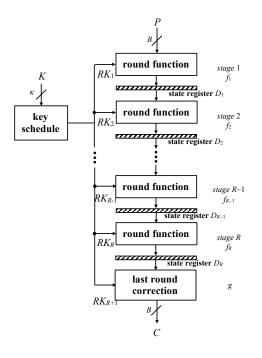

For SPNs and many other block ciphers, the structure of the cipher is iterative, comprised of a number of rounds, R, of simple cryptographic operations. For SPNs, these simple operations are the round function, which consists of round key mixing, substitution, and permutation. As per Shannon's product cipher proposal, the round function is executed iteratively an appropriate number of times to ensure confidence in the security of the cipher.

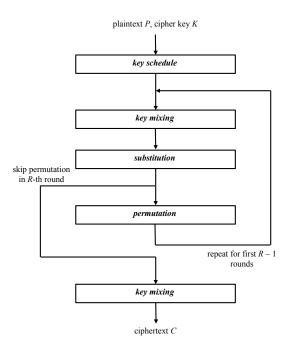

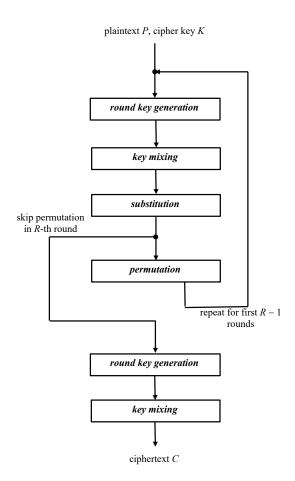

Typical structures of SPN block ciphers are illustrated in Figure 1.7 and Figure 1.8. The difference between the two diagrams is the nature of the application of the key schedule. In Figure 1.7, the key schedule algorithm is applied before the execution of the cipher rounds

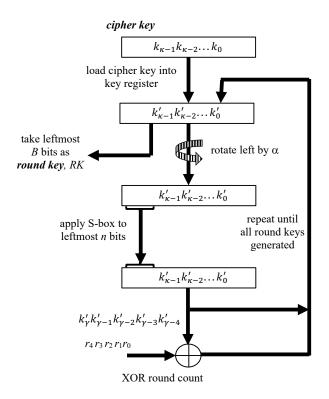

Figure 1.7: Encryption Structure with Round Key Setup

by the *key schedule* operation. Hence, in this case, all round keys are generated and stored for use during the processing of the cipher data. We refer to this approach as the *round key setup* approach. In contrast, in Figure 1.8, the *on-the-fly* approach to the key scheduling algorithm is illustrated, where the steps of the key schedule are executed within the cipher round by the *round key generation* operation, which produces the round key for use within the round. In this case, only one round key needs to be generated at a time and no storage of round keys is necessary. Instead, the key state is stored (from which the round key is computed) and is updated in each step of the algorithm. The on-the-fly approach is particularly of interest in hardware implementations where memory to store all round keys may be too costly and where it is possible to execute the key scheduling step in each round concurrently with the data processing operations, thereby improving the speed of the cipher execution.

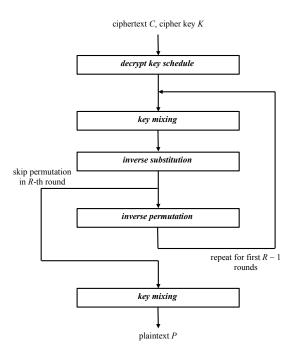

For the decryption of ciphertext, very similar structures can be used. For example, Figure 1.9 illustrates the strategy of the round key setup before execution of the rounds. The *decrypt key schedule* operation is similar the key schedule used for encryption, except some adjustments need to be made to the round key bit positions and the round keys must be applied in the reverse order to encryption, as discussed in Section 1.3.1, to ensure that the same structure is used for decryption as encryption. Also, the inverses of the substitution and permutation layers, *inverse substitution* and *inverse permutation*, must be used. For some ciphers, like the 16-bit and 64-bit SPNs of Figures 1.1 and 1.3, the inverse permutation is identical to the original permutation. The key mixing layer, due the property of the XOR

Figure 1.8: Encryption Structure with On-the-Fly Round Key Generation

function, is the same for decryption as for encryption.

We use these two general structures of (1) round key setup and (2) on-the-fly round key generation as the basis for our discussions of the implementation of ciphers in software and hardware.

## 1.6 Summary

In this chapter, we have presented the basic notions associated with block ciphers. Specifically, we have described the concept of the substitution-permutation network, one of the basic architectures used to implement block ciphers. We have presented concrete examples of a toy 16-bit SPN and a practical 64-bit SPN. The 64-bit SPN is, in fact, the same architecture as the lightweight cipher, PRESENT. We have also given the S-box from PRESENT as an

Figure 1.9: Decryption Structure with Round Key Setup

example component used in the cipher.

This chapter has also introduced the notion of the mode of operation of a block cipher and we shall see that often the mode applied to a cipher influences the selection of the implementation method (and possibly vice versa). Finally, we have illustrated the general iterative structure of the SPN and discussed how the key schedule can be implemented in either a setup phase or on-the-fly during the processing of the cipher rounds.

In the next chapter, we will delve into the practical implementation of block ciphers by considering the software implementation of the SPN focusing on general methodologies such as table lookups and bit-slicing structures.

## Chapter 2

## Software Implementation

In this chapter, we outline some of the principles and methods with which a designer could implement a block cipher in software. We focus on general concepts and do not delve into presenting any specific coding examples. Instead, we use pseudocode, descriptions, and examples to illustrate concepts. In doing so, we presume the availability of typical instructions that are found in all processors and refrain from discussing implementation issues related to specific processor instructions which might be helpful in cipher implementation but which are not ubiquitously found in computing environments.

### 2.1 Structure of Encryption

Since block ciphers, such as SPNs, are iterative in structure, they can be easily structured in a software program using "for" loops as shown in the pseudocode presented in Algorithm 1, where D is used to represent the cipher state. In the pseudocode, the round key setup approach is used for key scheduling so that round key values are generated prior to the processing of the plaintext data. This is done by calling KEYSCHED which produces and stores the data for the round key array,  $[RK_1, RK_2, ..., RK_R, RK_{R+1}]$ , based on the initial cipher key. This pseudocode is analogous the structure of Figure 1.7.

The pseudocode developed from the structure of Figure 1.8, with on-the-fly round key generation, is given in Algorithm 2. Here the steps of the key scheduling algorithm are placed within the body of the loop by calling function ROUNDKEY\_GENERATE. Hence, it is not necessary to store the complete set of round keys but to just produce the round key required for the current round based on the key state.

For an R round cipher, the body of the loop in both Algorithm 1 and Algorithm 2 performs the round operations and the loop is iterated R - 1 times, with the R-th round (which replaces the permutation with a key mixing) following the loop. In software, the functions KEYMIX, SUBSTITUTION, and PERMUTATION can be implemented using various methods, with the method selected based on an objective associated with the implementation, such as maximizing speed or minimizing storage. The implementation of these operations will be discussed in upcoming sections.

The key setup strategy of Algorithm 1 could be used when high speeds for software

| Algorithm 1 Pseudocode for Encrypt                | on with Round Key Setup                                          |

|---------------------------------------------------|------------------------------------------------------------------|

| function ENCRYPT $(P, K)$                         | $\triangleright$ inputs: plaintext P and cipher key K            |

| $[RK_1, RK_2,, RK_R, RK_{R+1}] \leftarrow 1$      | EYSCHED(K) 		 round keys                                         |

| $D \leftarrow P$                                  | $\triangleright$ load P into cipher state D                      |

| for $r = 1$ to $R - 1$ do                         |                                                                  |

| $D \leftarrow \text{keymix}(D, RK_r)$             |                                                                  |

| $D \leftarrow \text{SUBSTITUTION}(D)$             |                                                                  |

| $D \leftarrow \text{PERMUTATION}(D)$              |                                                                  |

| end for                                           |                                                                  |

| $D \leftarrow \text{Keymix}(D, RK_R)$             |                                                                  |

| $D \leftarrow \text{SUBSTITUTION}(D)$             |                                                                  |

| $D \leftarrow \operatorname{keymix}(D, RK_{R+1})$ | $\triangleright$ last round replaces permutation with key mixing |

| $\mathbf{return} \ D$                             | $\triangleright$ output: ciphertext $C$                          |

| end function                                      |                                                                  |

implementations are required, since the key schedule algorithm only needs to be executed once, before the encryption of all plaintexts to be encrypted under the key. The tradeoff is that all round keys must be stored for use, which requires more memory and this may be an issue in a tightly constrained system such as those found in some IoT devices. Using the on-the-fly key scheduling strategy of Algorithm 2 will be clearly slower in software, since extra operations in ROUNDKEY\_GENERATE must be executed for every pass of the loop for encryption of every plaintext. However, in this case, it is not necessary to store the full set of round keys and, hence, there may be advantages in environments with tight memory constraints but where speed of the encryption process is not an issue.

In subsequent sections, we discuss detailed characteristics of various implementation methods for the operations - key mixing, substitution, and permutation - within the round function. Although we have referred to the cipher state as D in the pseudocode described in this section, for convenience, in our description of the layers, we shall often use different variables to represent the state based on which layer is taking the state as input or producing the state as output. In particular, we shall use the following labels. The state at the input of the substitution (and output of the key mixing), we shall label as  $X = [x_{B-1}x_{B-2}...x_0]$ . The state at the output of the substitution and input to the permutation is labelled as  $Y = [y_{B-1}y_{B-2}...y_0]$ , while the state at the output of the permutation (and input of the key mixing) shall be referred to as  $Z = [z_{B-1}z_{B-2}...z_0]$ . For clarity, this is illustrated for one round of the 16-bit SPN in Figure 2.1.

#### 2.2Structure of Decryption

One of the advantages of the SPN architecture is that the decryption process is similar in structure to encryption and this is illustrated in Figure 1.9.

In Algorithm 3, we present the pseudocode for the decryption process and it can be seen that the layers use inverse operations (specifically the S-box and permutation operations INV\_SUBSTITUTION and INV\_PERMUTATION) as appropriate. Also notably, the round keys for the decryption process, represented as  $RK_r^*$ , require the application of the round keys

Algorithm 2 Pseudocode for Encryption with On-the-Fly Key Generation

function ENCRYPT(P, K) $\triangleright$  inputs: plaintext P and cipher key K  $D \leftarrow P$  $\triangleright$  load P into cipher state D  $K' \leftarrow K$  $\triangleright$  load K into key state K' for r = 1 to R - 1 do  $RK_r \leftarrow \text{ROUNDKEY}_\text{GENERATE}(K', r)$  $\triangleright$  update K' in function  $D \leftarrow \text{KEYMIX}(D, RK_r)$  $D \leftarrow \text{SUBSTITUTION}(D)$  $D \leftarrow \text{PERMUTATION}(D)$ end for  $RK_R \leftarrow \text{ROUNDKEY}_\text{GENERATE}(K', R)$  $D \leftarrow \text{KEYMIX}(D, RK_R)$  $D \leftarrow \text{SUBSTITUTION}(D)$  $RK_{R+1} \leftarrow \text{ROUNDKEY}_\text{GENERATE}(K', R+1)$  $D \leftarrow \text{KEYMIX}(D, RK_{R+1})$  $\triangleright$  last round replaces permutation with key mixing return D $\triangleright$  output: ciphertext C end function

Figure 2.1: SPN Round with Notation

from encryption in reverse order and with some adjustments made in the bit positions. For example, the round key for round R + 1 of encryption,  $RK_{R+1}$  is used as the round key for round 1 of decryption,  $RK_1^*$ . Round key  $RK_R$  of encryption is used as the round key of round 2 of decryption,  $RK_2^*$  (with adjustments to bit ordering);  $RK_{R-1}$  with reordered bits is used for  $RK_3^*$ , etc.

We now turn our focus to the operations involved in both encryption and decryption and discuss their software implementation.

## 2.3 Direct Implementation of an SPN

We begin by considering the straightforward, and largely impractical, approach of directly implementing an SPN in software. By direct implementation, we refer to the concept of executing the functionality of the operations explicitly in software. In the following sections,

Algorithm 3 Pseudocode for Decryption with Round Key Setup

function DECRYPT(C, K) $\triangleright$  inputs: ciphertext C and cipher key K  $[RK_1^*, RK_2^*, ..., RK_R^*, RK_{R+1}^*] \leftarrow \text{DEC}_{\text{KEYSCHED}}(K)$  $\triangleright$  generate round keys  $\triangleright$  load C into cipher state D  $D \leftarrow C$ for r = 1 to R - 1 do  $D \leftarrow \text{KEYMIX}(D, RK_r^*)$  $D \leftarrow \text{INV\_SUBSTITUTION}(D)$  $D \leftarrow \text{INV}_{\text{PERMUTATION}}(D)$ end for  $D \leftarrow \text{KEYMIX}(D, RK_B^*)$  $D \leftarrow \text{INV\_SUBSTITUTION}(D)$  $D \leftarrow \text{keymix}(D, RK^*_{R+1})$  $\triangleright$  last round replaces permutation with key mixing return D $\triangleright$  output: plaintext P end function

we will discuss much more practical and efficient approaches to software implementation using wide table lookups and bit-slicing.

### 2.3.1 Key Mixing Layer Implementation

The key mixing layer is typically the bitwise XOR of round key bits (derived by the key schedule) with the cipher state bits. In software this can be done very efficiently since processors have the bitwise XOR instruction than can be executed with two word inputs. If the cipher block size exceeds the processor word size, then multiple XOR operations may be needed. For example, for a 64-bit block size in an 8-bit processor, the XOR operation would need to be executed 8 times to mix a 64-bit round key with the 64-bit cipher state.

#### 2.3.2 Substitution Layer Implementation

Direct implementation of the S-box in software implies the use of a lookup table to mimic an S-box like the one of Table1.1. For the 4-bit S-box discussed in this paper, a direct implementation would require a table of  $2^4$  4-bit values, where a 4-bit value in the table represents the 4-bit output of the S-box which is indexed by the 4-bit input to the S-box. We refer to this approach as the *narrow table lookup*. It is straightforward in code to represent the data in the system using integers. However, because the S-boxes work on 4-bit sub-blocks of the larger block, care must be taken to extract the 4-bit inputs and move data into the correct position within the block for each of the S-box lookups. We describe the process of table lookups in more detail in Section 2.4.

#### 2.3.3 Permutation Layer Implementation

The permutation operation does not obviously lend itself well to direct implementation in software. In a straightforward approach, an implementation could process each bit by using a mask to isolate the bit, shifting it to an appropriate position and then combining it back into the output being constructed. We refer to this as the *bit rotation* method for permutation

implementation. For example, consider the leftmost 2 bits entering the 16-bit permutation of Table 1.2. Assume the input to the permutation is the 16-bit state Y and the 16-bit output state is Z. The two bits,  $y_{15}$  and  $y_{14}$ , are assigned to outputs as follows:  $z_{15} \leftarrow y_{15}$  and  $z_{11} \leftarrow y_{14}$ . This can be done by initializing Z to all zeroes. Then, assign Y to a temporary 16-bit variable of the state, W, and mask the leftmost bit by ANDing W with 8000<sub>16</sub>. XOR the result with Z to produce  $Z = [y_{15}00...00]$ . Next, assign Y again to W, mask the second bit using 4000<sub>16</sub>, shift 3 bits to the right to generate  $W = [0000y_{14}0...00]$ , which when XORed with Z produces  $Z = [y_{15}000y_{14}...00]$ .<sup>1</sup> This can be repeated to move, very inefficiently, all 16 bits of the state, according to the permutation. The bit rotation method is generally a poor choice to implement the permutation, although some modern processors have data manipulation instructions that may allow an improvement in the efficiency of the approach.

## 2.4 Table Lookup Implementations

In order to improve the efficiency of the software implementation of an SPN, one could make much more extensive use of table lookups. As we discussed in the previous section, S-boxes are naturally implemented as table lookups and, in this section, we will discuss how they can be conveniently combined with a lookup for the permutation. The other layer in a round, key mixing, is efficiently done using bitwise XOR on data blocks and does not need to involve table operations.

### 2.4.1 Permutation in a Table

Generally, since the bit rotation implementation approach requires operations on all bits of the block, it is not efficient on large blocks (typically, 64 or 128 bits) used for a practical block cipher. A much more efficient method for the permutation would be a *table lookup* approach. For the 16-bit SPN, the table lookup approach would make use of four tables, each consisting of  $2^4$  16-bit values, where each value represents the output of the permutation with appropriate input bits moved to the correct locations within the 16 output. For example, one of four tables will correspond to the leftmost nibble of the input Y, that is,  $[y_{15}y_{14}y_{13}y_{12}]$ . The table associated with the permutation of the bits in this nibble is presented in Table 2.1. A lookup in this table returns a 16-bit result,  $Z_1$ , of the form:  $Z_1 =$  $[y_{15}000y_{14}000y_{13}000y_{12}000]$ . Similarly, three other results from table lookups are produced using the other three input nibbles as indices into the 3 other tables producing outputs:  $Z_2 =$  $[0y_{11}000y_{10}000y_9000y_800], Z_3 = [00y_7000y_6000y_5000y_40], \text{ and } Z_3 = [000y_3000y_2000y_1000y_0].$ The output of the permutation is produced by isolating the 4 nibbles of Y (using shifts and masks as appropriate), using the nibbles as indices, looking up values in the 4 tables to retrieve  $Z_1, Z_2, Z_3$ , and  $Z_4$ , and generating the permutation output using bitwise XORing of the retrieved words:  $Y = Z_1 \oplus Z_2 \oplus Z_3 \oplus Z_4$ . This is much more efficient that individually moving the bits around, particularly for realistic block sizes.

Now, considering that the most efficient approaches to implement the S-box operation and the permutation both involve table lookups, it perhaps make sense to combine the tables

<sup>&</sup>lt;sup>1</sup>At many points within this article, we shall refer to the mixing of data in different bit positions together using the bitwise XOR operation on two words. However, this can also be done using a bitwise OR operation.

| Output                                  |

|-----------------------------------------|

| $Z_1$                                   |

| 000000000000000000000000000000000000000 |

| 0000000000001000                        |

| 00000001000000                          |

| 000000010001000                         |

| 0000100000000000                        |

| 000010000001000                         |

| 0000100010000000                        |

| 0000100010001000                        |

| 100000000000000000000000000000000000000 |

| 100000000001000                         |

| 10000001000000                          |

| 100000010001000                         |

| 100010000000000                         |

| 100010000001000                         |

| 1000100010000000                        |

| 1000100010001000                        |

|                                         |

Table 2.1: Permutation Table for Leftmost Nibble (All values in binary.)

into one table and complete the combination of the substitution and permutation operations with only one table lookup. This is described in the next section.

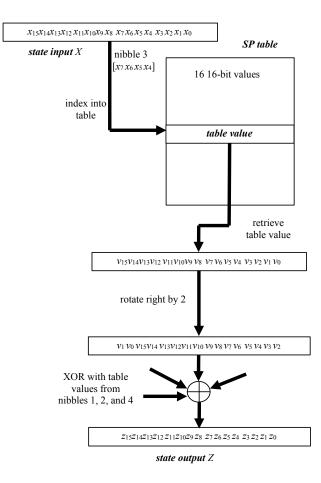

### 2.4.2 Combined Substitution/Permutation Table

An efficient implementation of both S-box and permutation is accomplished by combining both the S-box and permutation operations into table lookups where the values stored in the table are not the size of the S-box output, but the size of the block. We refer to this as the *wide table lookup* method.<sup>2</sup> Consider, for example, the leftmost bits of the 16-bit state at the input to the substitution layer,  $[x_{15}x_{14}x_{13}x_{12}]$ . The S-box operation results in a 4 bit output,  $[y_{15}y_{14}y_{13}y_{12}]$ , which, at the output of the permutation (from Table 1.2) would move these bits into the positions in the block as follows:

$y_{15} - - - y_{14} - - - y_{13} - - - y_{12} - - -$

Hence, we construct a table (which we call a substitution/permutation table or *SP table*) of all 16 outputs of the S-box with values of size equal to the block size where the S-box outputs are moved into the appropriate positions within the block according to the permutation. Such a table for the leftmost nibble is given in Table 2.2. A lookup in this table returns a 16-bit result,  $Z_1$ , of the form:  $Z_1 = [y_{15}000y_{14}000y_{13}000y_{12}000]$ , where the  $y_i$  values represent the outputs of the leftmost S-box ( $S_1$  in Figure 1.1) for input  $[x_{15}x_{14}x_{13}x_{12}]$ . (The middle column in the table is the 4-bit output of the S-box.) Similarly, tables can be constructed

<sup>&</sup>lt;sup>2</sup>For AES, a similar approach is referred to as the T-table approach by the cipher's proponents [2].

| Input                        | S-box Output                 | Table Output                            |

|------------------------------|------------------------------|-----------------------------------------|

| $[x_{15}x_{14}x_{13}x_{12}]$ | $[y_{15}y_{14}y_{13}y_{12}]$ | $Z_1$                                   |

| (Table Index)                | (Intermediate Value)         | -                                       |

| 0000                         | 1100                         | 1000100000000000                        |

| 0001                         | 0101                         | 0000100000001000                        |

| 0010                         | 0110                         | 0000100010000000                        |

| 0011                         | 1011                         | 100000010001000                         |

| 0100                         | 1001                         | 100000000001000                         |

| 0101                         | 0000                         | 000000000000000000000000000000000000000 |

| 0110                         | 1010                         | 10000001000000                          |

| 0111                         | 1101                         | 100010000001000                         |

| 1000                         | 0011                         | 000000010001000                         |

| 1001                         | 1110                         | 1000100010000000                        |

| 1010                         | 1111                         | 1000100010001000                        |

| 1011                         | 1000                         | 100000000000000000000000000000000000000 |

| 1100                         | 0100                         | 0000100000000000                        |

| 1101                         | 0111                         | 0000100010001000                        |

| 1110                         | 0001                         | 0000000000001000                        |

| 1111                         | 0010                         | 00000001000000                          |

Table 2.2: SP Table for Leftmost S-box  $(S_1)$  Input (All values in binary.)

for the second, third and fourth S-boxes (nibbles  $[x_{11}x_{10}x_9x_8]$ ,  $[x_7x_6x_5x_4]$ , and  $[x_3x_2x_1x_0]$ ). Note that, although the S-box outputs are identical for identical inputs, four SP tables are used because the permutation results in different values for the table based on which S-box is receiving the input. For example, if the leftmost S-box,  $S_1$ , has input "0000", the SP table lookup results in an output of "100010000000000" (as can be seen in Table 2.2), while input "0000" to the S-box second from the left,  $S_2$  in Figure 1.1, results in an output of "0100010000000000" from the SP table lookup (not illustrated).

Determining the output of the combined substitution/permutation layers can be achieved by using the four S-box inputs to complete four table lookups similar to Table 2.2. The 4 blocks corresponding to the outputs of these lookups can then be combined to produce the output block of the combined operation by XORing the 4 blocks together. Since the blocks in the tables have "0"s in the bits which are not directly affected by the corresponding Sbox output, these bits have no effect in the XORing outcome and only the bits produced by the S-box output end up affecting the appropriate output block bit. The pseudocode representing the combined substitution/permutation operation based on wide table lookup using multiple lookup tables (4 in this example) is given in Algorithm 4. In the pseudocode, notation " $\oplus$ ", ".", and ">> i" represent bitwise XOR, bitwise AND, and right rotation by *i* bits, respectively. For right rotations, bits shifted out of the rightmost end of the variable are shifted into the leftmost end of the variable. Function SP\_LOOKUP(*i*, ·) represents a lookup in the SP table corresponding to S-box *i*. An example of the application of the pseudocode is given in Table 2.3.

| Algorithm 4 Pseudocode for SP Wide Table Lookup (Multiple Tables) |                                                          |  |  |  |

|-------------------------------------------------------------------|----------------------------------------------------------|--|--|--|

| <b>function</b> $SUB\_PERM(X)$ $\triangleright$ input: 16-bit sta |                                                          |  |  |  |

| $Z \leftarrow 0000_{16}$                                          |                                                          |  |  |  |

| for $i = 1$ to 4 do                                               |                                                          |  |  |  |

| $W \leftarrow [X >> 4(4-i)] \cdot (000 \mathrm{F}_{16})$          | $\triangleright$ extract 4-bit bit index                 |  |  |  |

| $V \leftarrow \text{SP}\_\text{LOOKUP}(i, W)$                     | $\triangleright$ perform 4-bit lookup in table <i>i</i>  |  |  |  |

| $Z \leftarrow Z \oplus V$                                         | $\triangleright$ combine 16-bit result into 16-bit state |  |  |  |

| end for                                                           |                                                          |  |  |  |

| return $Z$                                                        | $\triangleright$ output: 16-bit state Z                  |  |  |  |

| end function                                                      |                                                          |  |  |  |

| Input $X = 7AF8$           | $Z \leftarrow 0000$                                            |

|----------------------------|----------------------------------------------------------------|

| i = 1                      | $W \leftarrow 7$                                               |

|                            | $V \leftarrow \text{SP}_{\text{LOOKUP}}(1,7) = 8808$           |

|                            | $Z \leftarrow 0000 \oplus 8808 = 8808$                         |

| i = 2                      | $W \leftarrow \mathbf{A}$                                      |

|                            | $V \leftarrow \text{SP}_{\text{LOOKUP}}(2, \mathbf{A}) = 4444$ |

|                            | $Z \leftarrow 8808 \oplus 4444 = \text{CC4C}$                  |

| i = 3                      | $W \leftarrow \mathbf{F}$                                      |

|                            | $V \leftarrow \text{SP}_{\text{LOOKUP}}(3, F) = 0020$          |

|                            | $Z \leftarrow \mathrm{CC4C} \oplus 0020 = \mathrm{CC6C}$       |

| i = 4                      | $W \leftarrow 8$                                               |

|                            | $V \leftarrow \text{SP}_{\text{LOOKUP}}(4, 8) = 0011$          |

|                            | $Z \leftarrow \text{CC6C} \oplus 0011 = \text{CC7D}$           |

| Output $Z = \mathbf{CC7D}$ |                                                                |

Table 2.3: Example of Wide Table Lookup (Multiple Tables) (All values in hexadecimal.)

For the case discussed above, 4 tables are required, each consisting of 16 values of size 16 bits. Hence, a minimum total of  $4 \times 16 = 64$  16-bit words must be stored.<sup>3</sup> This is compared to the memory requirement of 16 nibbles if simply the S-box is stored for the narrow table lookup approached mentioned in Section 2.3.2.

In some cases, such as for the 16-bit SPN, the memory requirement for the combined substitution/permutation method can be reduced further noting that the values in the 4 different SP tables associated with each S-box position are simply rotations of the table for the leftmost S-box. For example, all values in the table for the S-box that is second from the left,  $S_2$ , are the same as the values for the leftmost S-box shifted right by one bit. Hence, for input "0000" to  $S_1$ , the table output is "100010000000000", while for input '0000" to  $S_2$ , the table output is "010001000000000". As a result, we do not need to store 4 tables, but can store one table and then with a rotation operation produce the appropriate 16-bit value to

$<sup>^{3}</sup>$ Of course, this total could also be enumerated as 256 nibbles or 128 bytes. Also it should be noted that how much is allocated for a table is dependent on how the table is stored in memory. For example, a 16-bit table value might be conveniently stored as a 32-bit integer, resulting in twice as many nibbles (bytes) being used.

Figure 2.2: SP Wide Table Lookup Using Single Table

be used in the production of the round output block. The memory size of the required table can now be 16 16-bit words (or, equivalently, 64 (32) nibbles (bytes)). The penalty for this saving of memory is the additional rotation operation required for each lookup. The process for the wide table lookup using a single table is illustrated in Figure 2.2. In the figure, it is shown how the nibble that is 2nd from the right is used as an index into the table, following which the retrieved value is rotated right by 2 positions. The resulting output, combined using XOR with the lookup/rotations from the other 3 nibbles of the state is the new state value at the output of the round.

## 2.5 Time/Memory Tradeoffs of Lookup Tables

Consider now a generalized perspective on the memory requirements and speed associated with the combined substitution/permutation wide table lookup approach. Assume that an SPN is constructed using *n*-bit S-boxes and that the block size is B. Also, let  $\omega$  represent the size of word used in the processor for instruction operands and storage of data.

Consider first the direct implementation of the SPN using the narrow table lookup discussed in Section 2.3.2 for the S-box followed by bit rotation approach for the permutation implementation. Such an implementation would use one table for the S-box of size  $2^n$  words, where we assume that each value in the table would take a full word, even though typically  $\omega > n$ .<sup>4</sup> Using the bit rotation method for the permutation operation would require operations on all *B* bits of the block.