# High-Speed Hardware Architectures and FPGA Benchmarking of CRYSTALS-Kyber, NTRU, and Saber

Viet Ba Dang, Kamyar Mohajerani and Kris Gaj

Cryptographic Engineering Research Group, George Mason University Fairfax, VA, U.S.A.

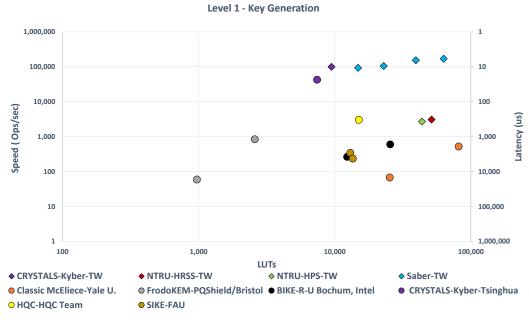

**Abstract.** Performance in hardware has typically played a significant role in differentiating among leading candidates in cryptographic standardization efforts. Winners of two past NIST cryptographic contests (Rijndael in case of AES and Keccak in case of SHA-3) were ranked consistently among the two fastest candidates when implemented using FPGAs and ASICs. Hardware implementations of cryptographic operations may quite easily outperform software implementations for at least a subset of major performance metrics, such as latency, number of operations per second, power consumption, and energy usage, as well as in terms of security against physical attacks, including side-channel analysis. Using hardware also permits much higher flexibility in trading one subset of these properties for another. This paper presents high-speed hardware architectures for four lattice-based CCA-secure Key Encapsulation Mechanisms (KEMs), representing three NIST PQC finalists: CRYSTALS-Kyber, NTRU (with two distinct variants, NTRU-HPS and NTRU-HRSS), and Saber. We rank these candidates among each other and compare them with all other Round 3 KEMs based on the data from the previously reported work.

**Keywords:** Post-Quantum Cryptography  $\,\cdot\,$  lattice-based  $\,\cdot\,$  Key Encapsulation Mechanism  $\,\cdot\,$  hardware  $\,\cdot\,$  FPGA

# 1 Introduction

Post-Quantum Cryptography (PQC) refers to a class of cryptographic algorithms that are resistant against all known attacks using quantum computers and can be implemented on traditional non-quantum computing platforms. These platforms include microprocessors, microcontrollers, graphics processing units (GPUs), Field Programmable Gate Arrays (FPGAs), Application-Specific Integrated Circuits (ASICs), and many others. The main goal of PQC is to replace the existing public-key cryptography standards based on RSA and Elliptic Curve Cryptography. These standards seem to be the most vulnerable to quantum computing and impossible to defend using traditional approaches such as gradually increasing key sizes [86, 14, 90, 39].

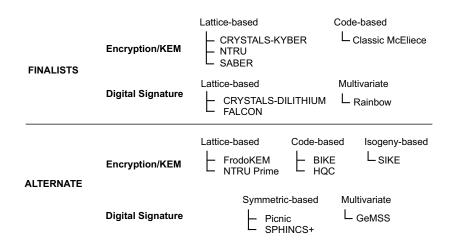

To initiate a timely transition to a new class of cryptographic schemes, in December 2016, NIST launched its PQC standardization process with the release of a "Call for Proposals and Request for Nominations for Public-Key Post-Quantum Cryptographic Algorithms" [72]. Sixty-nine submissions were judged complete and accepted for Round 1, which started in December 2017 [78, 1]. In January 2019, based on the initial security analysis and preliminary software benchmarking results, 26 submissions were qualified by NIST to Round 2. On July 22, 2020, NIST announced 15 candidates qualified for Round 3 of the standardization process. These candidates are summarized in Fig. 1. All

Figure 1: Finalists and alternate candidates qualified to Round 3 of the NIST PQC Standardization Process

Round 3 candidates represent five diverse families: lattice-based, code-based, multivariate, symmetric-based, and isogeny-based. Seven finalists are expected to be given priority in the standardization process. One encryption/KEM scheme and one digital signature scheme from this group may be selected as a PQC standard as early as 2022. Alternate candidates are treated as backup candidates. In Round 2, alternate candidates were judged to be either insufficiently investigated from the security point of view or were believed to lack some desired properties related to their performance (such as small public keys, small signatures, short execution time in software, etc.).

Hardware benchmarking has played a major role in all recent cryptographic standardization efforts, such as the AES, eSTREAM, SHA-3 [8, 37, 55, 57], and CAESAR contests [17, 20]. With the emergence of commonly-accepted hardware application programming interfaces (APIs) [43], development packages [42, 46], specialized optimization tools [38, 28], new design methodologies based on High-Level Synthesis (HLS) [44, 45], and mandatory hardware implementations in the final round of the CAESAR contest [17], the percentage of initial submissions implemented in hardware grew from 27.5% in the SHA-3 contest [36] to 49.1% in the CAESAR competition [20, 35]. Unfortunately, this trend could not be sustained in the NIST PQC standardization process. In many respects, PQC schemes are diametrically different and at least an order of magnitude more complex to implement compared to those evaluated in previous cryptographic contests.

### Choice of Algorithms to Implement.

There are only four KEM PQC finalists. Since the NIST announcement in July 2020, it is urgent to compare them against each other. In particular, NIST is tentatively planning to choose only one of these candidates for the first round of standardization at the end of 2021 or at the beginning of 2022. The excellent implementation of Classic McEliece was reported in 2017-2018. Thus, the efficient implementations of the remaining three KEM finalists are of utmost importance at this point. Consequently, in this paper, we aim at evaluating and contrasting the hardware efficiency of CRYSTALS-KYBER, NTRU, and Saber.

In terms of algorithm types, we focus on KEMs with indistinguishability under a chosen-ciphertext attack (IND-CCA). Our primary goal was to implement all lattice-based IND-CCA secure KEMs described in the specifications of PQC finalists. The submission package of NTRU describes two substantially different KEMs : NTRU-HRSS and NTRU-HPS. As a result, we have implemented four KEMs representing three PQC finalists. For each implemented KEM, we generated results for all supported security levels.

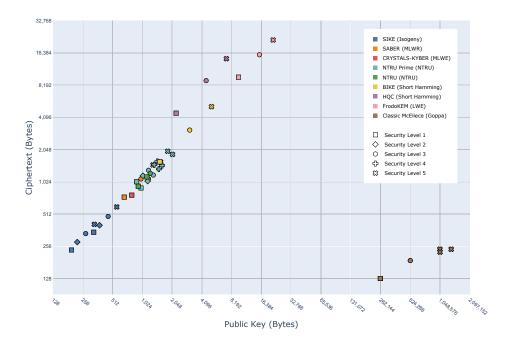

Figure 2: Relation between the ciphertext and public-key sizes for Round 3 PQC Key Encapsulation Mechanisms

In Fig. 2, we show the relationship between the ciphertext and public-key sizes of all Round 3 candidates. All schemes based on structured lattices - Saber, CRYSTALS-KYBER, NTRU Prime, and NTRU - have their ciphertext and public key sizes in the range between 512 and 2048 bytes. The only candidate better than them is an isogeny-based SIKE, which is still considered relatively recent and not sufficiently scrutinized from the security point of view. As a result, this scheme was qualified for Round 3 only as an alternate candidate. The only other PKE/KEM finalist, Classic McEliece, has public-key lengths between 0.25 and 2 Megabytes. So large public key sizes may significantly impact the sizes of data exchanged between two parties in the key establishment phase of any modern secure communication protocol, such as TLS, IPSec, SSH, etc. The sizes of keys and ciphertexts used by the selected lattice-based schemes are significantly smaller than those of the alternate code-based schemes, BIKE and HQC, and the unstructured-lattice scheme FrodoKEM. As a result, the key establishment time and the amount of memory required to store public-key certificates are also the most practical among all Round 3 candidates other than SIKE.

**High-speed vs. lightweight.** Assuming comparable technology, hardware implementations outperform software implementations using at least one, and typically multiple, metrics, such as latency, number of operations per second, power consumption, energy usage, and security against physical attacks. They also allow much higher flexibility in trading one subset of these metrics for another. From the point of view of benchmarking and ranking of candidates, such flexibility may become a curse, especially considering that no two metrics are likely to have a simple linear dependence on each other. A practical solution to this problem is to focus during the evaluation process on two major types of implementations: high-speed and lightweight.

In high-speed implementations, the primary target is speed, understood as either minimum latency (a.k.a. execution time) or the number of operations per second. For PQC schemes, this target amounts to optimizing the implementations of major operations involving the public and private key, respectively. For Key Encapsulation Mechanisms (KEMs), these operations are encapsulation and decapsulation; for digital signature schemes, signature verification and generation; for public-key encryption (PKE), encryption and decryption. The time of key generation may also play a major role in the case when a public-private key pair cannot be reused for security reasons. The resource utilization is secondary. Still, hardware designers typically aim at achieving the Pareto optimality, in which any further speed improvement comes at a disproportionate cost in terms of resource utilization.

In lightweight implementations, the primary targets are typically minimum resource utilization and minimum power consumption, assuming that the execution time does not exceed a predefined maximum. Another way of formulating the goal is to achieve minimum execution time, assuming a given maximum budget in terms of resource utilization, power consumption, or energy usage. The maximum budget on resource utilization is related to the cost of implementation; the budget on power assures correct operation without overheating or devoting additional resources to cooling. The maximum energy usage affects how long a battery-operated device can function before the next battery recharge. In the context of the standardization process for cryptographic algorithms, the mentioned above maximum budgets are very hard to select. Any change in these thresholds may favor a different subset of candidates. With new standards remaining in use for decades, the timing, cost, and power requirements of new and emerging applications are very challenging to predict. Additionally, lightweight hardware implementations can outperform only software implementations targeting specific low-cost, low-power embedded processors, such as Cortex-M4. As a result, in this paper, we focus on developing, benchmarking, and ranking high-speed implementations.

**Design Methodology.** Hardware design methodologies are developed by the industry over the period of decades. The Register-Transfer Level (RTL) methodology is the most popular design methodology codified by academic textbooks and supported by most industry-grade computer-aided design tools. This methodology assumes designing/coding at a level that is manageable for humans and easy for tools to turn into efficient hardware. The entire system is divided into the Datapath and Controller. The Datapath is described using a hierarchical block diagram using medium-scale components (e.g., adders, multipliers, multiplexers, registers, and memories). The Controller is described using hierarchical algorithmic state machine (ASM) charts or state diagrams. Indirectly, the designer specifies what happens in the circuit in every clock cycle. Thus, the latency (the execution time of a particular major operation) in clock cycles is an inherent feature of the design. The tools determine the maximum clock frequency at which the circuit can operate and the amount of hardware resources used.

Any other approaches to hardware design are often mistrusted. In some cases, justifiably so. For example, recent attempts at replacing RTL with High-Level Synthesis resulted in PQC designs 2-4 orders of magnitude less efficient [13, 21]. Similarly, the use of the software/hardware co-design for PQC led to inconclusive results disregarded by NIST at the end of Round 2 [21, 2]. Therefore, the development of hardware implementations described in this paper follows the traditional RTL methodology.

Our Contributions. The main contributions of this paper are summarized below:

- 1. we have proposed, documented, and designed the first complete hardware implementations of two variants of NTRU (NTRU-HRSS and NTRU-HPS), as defined in the submissions to Rounds 2 and 3 of the NIST PQC standardization process

- 2. we have developed a new hardware implementation of CRYSTALS-KYBER outperforming the best previous design in terms of latency, number of operations per second, and the product of latency  $\times$  #LUTs.

- 3. we have developed four new implementations of Saber. For the security level 3, two of them outperform the best previous design in terms of resource utilization. The

| Algorithms       | Hardware               | Software/Hardware              |

|------------------|------------------------|--------------------------------|

|                  | Lattice-based          |                                |

| CRYSTALS-KYBER   | $[13]^H, [49], [95]$   | $[9], [10]^*, [33], [3], [94]$ |

| FrodoKEM         | $[47], [13]^H,$        | $[22], [9], [10]^*$            |

| NTRU             | $[13]^{H}$             | _                              |

| NTRU Prime       | [66], [76]             | _                              |

| Saber            | $[13]^{H}, [87], [98]$ | [22], [68], [33]               |

|                  | Isogeny-based          |                                |

| SIKE             | [59], [26]             | [67]                           |

|                  | Code-based             |                                |

| BIKE             | [48], [79], [82], [81] | _                              |

| Classic McEliece | $[92], [91], [13]^H$   | _                              |

| HQC              | $[83]^H$               | _                              |

| 77               |                        |                                |

Table 1: Reported Hardware and Software/Hardware Implementations of KEMs qualified to Round 3

$^{H}$  design developed using the High-Level Synthesis (HLS) approach \* extended version of [9]

other two have higher resource utilization but are significantly faster.

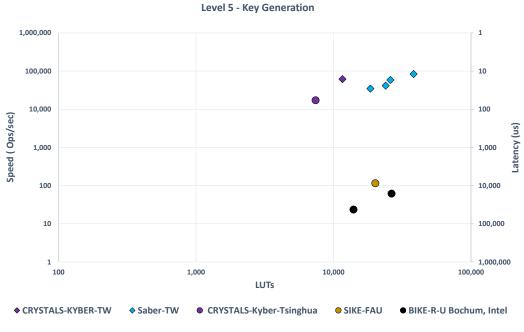

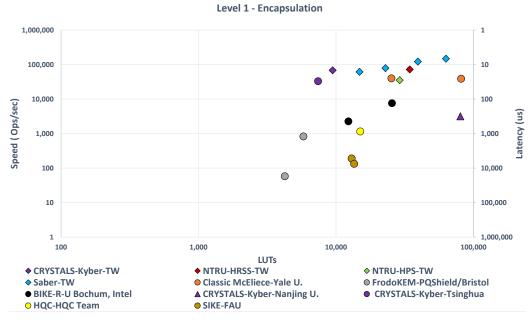

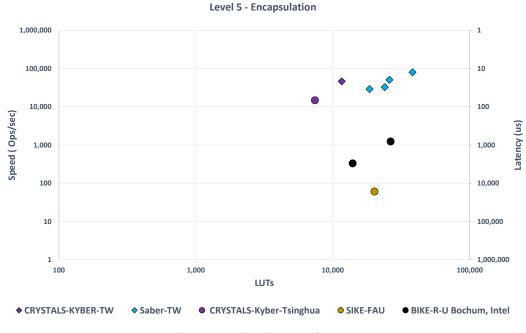

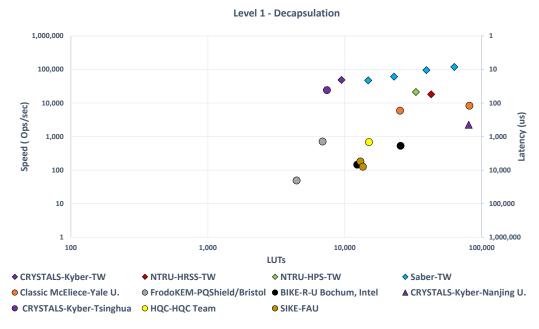

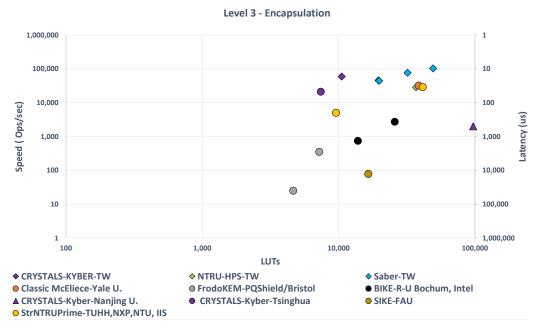

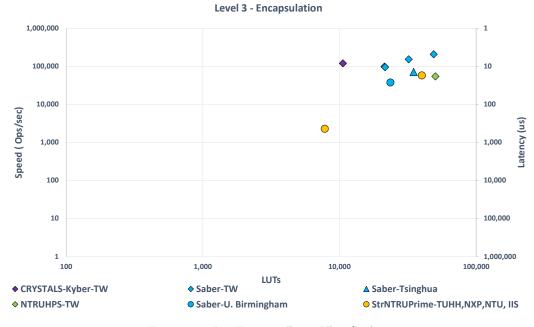

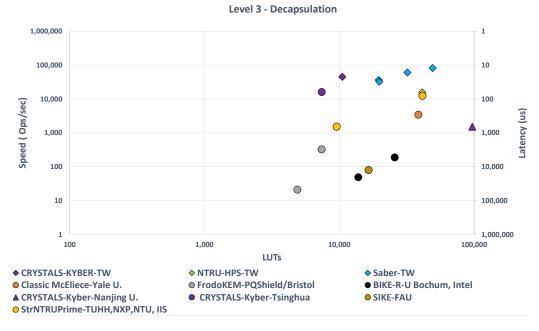

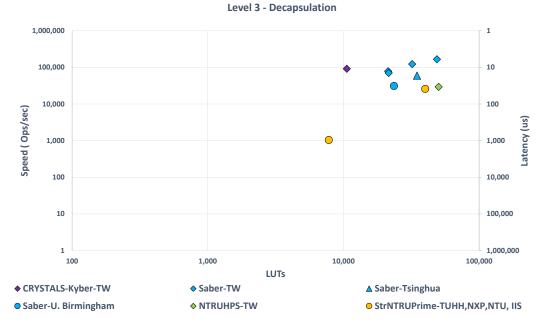

4. we benchmarked all mentioned above designs using two FPGA families and compared them with the earlier reported designs for all remaining Round 3 KEMs in terms of latency, the number of operations per second, and the number of LUTs.

All new designs reported in this paper are fully reproducible, and their source code will be released as open-source after the acceptance of this paper to a journal or a conference with proceedings.

## 2 Previous Work

Hardware and software/hardware implementations of all KEMs qualified to Round 3 of the NIST PQC Standardization Process are summarized in Table 1. The PQC candidates are grouped by family.

HLS-based implementations are distinguished with the superscript<sup>H</sup>. These implementations were reported in only one paper [13]. They have been shown to give substantially different results than implementations developed using traditional Register-Transfer Level (RTL) methodology, in which HDL code is developed manually. Therefore, in this paper, we focus on implementations in which a hardware part of the design was developed using traditional RTL methodology. NTRU (as specified in Rounds 2 and 3 of the NIST process) and HQC are the only candidates with no RTL implementations reported to date.

In particular relevance to this paper, we are unaware of any hardware implementation of either NTRU-HPS or NTRU-HRSS as defined during Rounds 2 and 3 of the PQC standardization process. Earlier versions of NTRU were significantly different. Therefore, all major building blocks, top-level block diagram, scheduling scheme, and the corresponding control unit had to be designed from scratch. Nevertheless, we would like to acknowledge earlier work on the implementation of NTRUEncrypt Short Vector Encryption Scheme (SVES), as defined in the IEEE 1363.1 Standard Specification for Public Key Cryptographic Techniques Based on Hard Problems over Lattices [51]. The most complete high-speed constant-time hardware implementation of this scheme is reported in [29]. Some of the major differences include the fact that NTRUEncrypt SVES is an encryption scheme rather than KEM. The underlying hash function is SHA-256 rather than SHA3-256. NTRUEncrypt SVES has a non-zero decryption failure rate. Decryption does not require polynomial multiplication in which both operands have only "large" coefficients. There is no notion of packing, unpacking, or lifting. All major parameters are substantially different. Additionally, the implementation reported in [29] does not support key generation in hardware. Another implementation of NTRUEncrypt SVES, reported in [62, 63], supports only encryption. All earlier hardware implementations of NTRU, such as those reported in [7, 74, 54, 5, 53], concerned variants that had even more differences as compared to the most recent specifications of NTRU-HPS and NTRU-HRSS.

The most similar hardware implementation of CRYSTALS-Kyber is described in [95]. Our project started before [95] was published. Major design decisions were made in 2020 based only on earlier available literature. These decisions differed in many aspects from those described in [95]. Some of the most important decisions included the use of k NTT multipliers vs. one used in [95]. Additionally, our design uses a different modular reduction unit, a much faster Keccak module, efficient NTT memory access, faster and smaller encoding and decoding units, and a more efficient rejection sampler. Unlike [95], our design is also technology independent by not employing any vendor-specific IPs. The detailed list of differences is provided in Section 5.2.7. The second pure hardware implementation of CRYSTALS-Kyber is reported in [49]. This implementation supports only encapsulation and decapsulation and is about an order of magnitude less efficient than the one reported in [95]. Earlier implementations of Kyber were of the software/hardware type, and many of them concerned a substantially different Round 1 version of this candidate.

The most similar hardware implementations of Saber are described in [87, 98]. Both designs follow an unified architecture approach that supports selecting parameter sets at run time. [87] employed a schoolbook-based multiplier meanwhile [98] proposed a hierarchical 8-level Karatsuba multiplier. [12] later improves area consumption of the high-speed multiplier in [87] and introduces a new lightweight architecture.

Major types of polynomial multipliers used in the hardware implementations of latticebased PQC schemes include Schoolbook, Karatsuba [56], Toom-Cook [89, 16], and NTTbased. NTT-based multipliers have been particularly popular in the last decade, and their various architectures and optimized implementations were reported in various publications, such as [77, 84, 24, 80, 75, 61, 96, 31, 97, 93]. Karatsuba and Toom-Cook multipliers have been used for the implementation of Saber. In particular, [98] used Karatsuba, and [68] explored the use of Toom-Cook. Schoolbook multipliers have been used for years, in particular in [77, 27, 64, 87], and many others.

# 3 Background

### 3.1 Basic Features of Compared Algorithms

Selected features of all implemented KEMs are summarized in Table 2. All three KEMs are based on the underlying IND-CPA public-key encryption (PKE) schemes. In CRYSTALS-Kyber and Saber, the conversions to the corresponding IND-CCA KEMs are performed using very similar variants of the Fujisaki–Okamoto (FO) transform [34], [41]. NTRU uses a generic transformation from a deterministic public-key encryption scheme to construct a KEM. The NTRU KEM transformation provides IND-CCA2 security with a tight reduction to the well-studied OW-CPA (one-way CPA) security of the NTRU PKE [85]. The only KEMs with no Decryption Failure in the underlying PKE are NTRU-based KEMs, NTRU-HPS, and NTRU-HRSS. Consequently, these schemes require no re-encryption during decapsulation.

In all of these KEMs, the elementary operation is multiplication mod q. In Saber,

| Feature                                            | CRYSTALS-Kyber                                                            | Saber                                                                                                                                                | NTRU-HPS                                                                                                                       | NTRU-HRSS                                                                                                                   |

|----------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Underlying<br>problem                              | Mod-LWE:<br>Module Learning<br>with Errors                                | Mod-LWR:<br>Module Learning<br>with Rounding                                                                                                         | SVP: Shortest Vector<br>Problem                                                                                                | SVP: Shortest Vector<br>Problem                                                                                             |

| Sampling                                           | Integers are sampled<br>from a centered<br>binomial distribution<br>(CBD) | Integers are sampled<br>from a centered<br>binomial distribution<br>(CBD)                                                                            | Fixed-weight and variable<br>-weight polynomials are<br>sampled from a<br>uniform distribution                                 | Variable-weight<br>polynomials are sampled<br>from a uniform<br>distribution                                                |

| Degree $n$                                         | Power of 2                                                                | Power of 2                                                                                                                                           | Prime                                                                                                                          | Prime                                                                                                                       |

| Modulus $q$                                        | Prime                                                                     | Power of 2                                                                                                                                           | Power of 2<br>with $q/8 - 2 \le 2n/3$                                                                                          | Power of 2<br>with $q > 8\sqrt{2}(n+1)$                                                                                     |

| Other major<br>parameters                          | k: number of<br>polynomials per vector,<br>$\eta$ : parameter of CBD      | $\begin{array}{c} p, \ T: \ \text{other moduli,} \\ l: \ \text{number of} \\ polynomials \ per \ vector, \\ \mu: \ parameter \ of \ CBD \end{array}$ | d: Fixed weight<br>for g and m<br>Lift $(m)$ : Identity $m \mapsto m$                                                          | $f, g: \text{ Non-negative} \\ \text{ correlation} \\ \text{ Lift}(m): \\ m \mapsto \Phi_1 \cdot S_3(m/\Phi_1) \end{cases}$ |

| Hash-based<br>functions                            | SHA3-256,<br>SHA3-512,<br>SHAKE128,<br>SHAKE256                           | SHA3-256,<br>SHA3-512,<br>SHAKE128                                                                                                                   | SHA3-256                                                                                                                       | SHA3-256                                                                                                                    |

| Decryption<br>failures                             | Yes                                                                       | Yes                                                                                                                                                  | No                                                                                                                             | No                                                                                                                          |

| Polynomial Rings                                   | $\mathbb{Z}_q[x]/(x^n+1)$                                                 | $\mathbb{Z}_q[x]/(x^n+1)$                                                                                                                            | $\begin{array}{c} {\rm R/q:} \ Z_q[x]/(x^n-1) \\ {\rm S/q:} \ Z_q[x]/(\Phi_n)^* \\ {\rm S/3:} \ Z_3[x]/(\Phi_n)^* \end{array}$ | $\begin{array}{c} {\rm R/q:} \ Z_q[x]/(x^n-1) \\ {\rm S/3:} \ Z_3[x]/(\Phi_n)^* \end{array}$                                |

| #Polynomial<br>Multiplications<br>in Encapsulation | $k^2 + k$                                                                 | $l^2 + l$                                                                                                                                            | 1 in $R/q$                                                                                                                     | 1 in $R/q$                                                                                                                  |

| #Polynomial<br>Multiplications<br>in Decapsulation | $k^{2} + 2k$                                                              | $l^{2} + 2l$                                                                                                                                         | 1 in R/q<br>1 in S/q<br>1 in S/3                                                                                               | 1 in R/q<br>1 in S/q<br>1 in S/3                                                                                            |

Table 2: Features of lattice-based NIST Round 3 finalists in the category of KEMs

\*  $\Phi_n = (x^n - 1)/(x - 1)$  irreducible in  $Z_q[x]$

NTRU-HPS, and NTRU-HRSS, q is a power of two, significantly simplifying the reduction mod q. In Kyber, q is a special prime, selected in such a way to support speeding up polynomial multiplication in  $\mathbb{Z}_q[x]/(x^n+1)$  using the Number Theoretic Transform (NTT).

All four algorithms use SHA3-256. Saber additionally employs SHA3-512 and SHAKE128. Kyber requires the same set of hash-based algorithms as Saber, extended with SHAKE256. NTRU-based KEMs use sampling from the uniform distribution. In Kyber and Saber, a Centered Binomial Distribution (CBD) is employed.

There are two variants of NTRU described in the specification, the NTRU-HPS based on Hoffstein, Pipher, and Silverman's NTRU encryption scheme [40] and NTRU-HRSS introduced by Hülsing, Rijnveld, Schanck, and Schwabe in [50]. The NTRU-HPS parameter sets follow the approach to use fixed-weight sample spaces and allow several choices of modulus q for each degree n. Meanwhile, the NTRU-HRSS allows arbitrary-weight sample spaces but restricts q as a function of n.

In Kyber and Saber, the most time-consuming operations are matrix-by-vector and vector-by-vector multiplications, where each element of a matrix or a vector is a polynomial with n coefficients in  $Z_q$ , and the multiplication of such polynomials is performed modulo the reduction polynomial  $x^n + 1$ . In the NTRU-based KEMs, the most time-consuming operation is polynomial multiplication in the rings specified in Table 2.

Parameter sets of three investigated candidates are summarized in Table 3. The specification of NTRU associates two different security categories with each parameter set of NTRU-HPS and NTRU-HRSS. In this paper, we conservatively assumed the lower security category based on the so-called non-local computational models (see [21], Section 5.3 Security Categories). The same computation model is implicitly assumed by the submitters of the other investigated algorithms. We implemented three parameter sets of NTRU-HPS and NTRU-HRSS, which are ntruhrss701, ntruhps2048677, and ntruhps4096821, corresponding to security levels 1, 1, and 3, respectively in non-local models of computation.

| Algorithm | Parameter      | Security | Degree | Modulus  | Sk Size | Pk Size | Ct Size |

|-----------|----------------|----------|--------|----------|---------|---------|---------|

| 0.0       | Set            | Level    | n      | q        | [bytes] | [bytes] | [bytes] |

| Kyber     | Kyber512       | 1        | 256    | 3329     | 1,632   | 800     | 768     |

| NTRU-HPS  | ntruhps2048677 | 1*       | 677    | $2^{11}$ | 1,235   | 931     | 931     |

| NTRU-HRSS | ntruhrss701    | 1*       | 701    | $2^{13}$ | 1,452   | 1,138   | 1,138   |

| Saber     | LightSaber-KEM | 1        | 256    | $2^{13}$ | 1,568   | 672     | 736     |

| Kyber     | Kyber768       | 3        | 256    | 3329     | 2,400   | 1,184   | 1,088   |

| NTRU-HPS  | ntruhps4096821 | 3*       | 821    | $2^{12}$ | 1,592   | 1,230   | 1,230   |

| Saber     | Saber-KEM      | 3        | 256    | $2^{13}$ | 2,304   | 992     | 1,088   |

| Kyber     | Kyber1024      | 5        | 256    | 3329     | 3,168   | 1,568   | 1,568   |

| Saber     | FireSaber-KEM  | 5        | 256    | $2^{13}$ | 3,040   | 1,312   | 1,472   |

Table 3: Parameter sets of investigated algorithms. Notation: Sk - Secret Key, Pk - Public key, Ct - Ciphertext.

\* assuming non-local computational models

### 3.2 Short Introductions to Compared Algorithms

### 3.2.1 NTRU

**Definitions and Parameters.**  $\Phi_1$  is (x-1).  $\Phi_n$  is  $(x^n-1)/\Phi_1 = x^{n-1} + x^{n-2} + \ldots + x+1$ . From the implementation point of view, all operations in NTRU are polynomial operations over the quotient rings  $R_q$ ,  $S_q$  and  $S_p$  where  $R_q : \mathbb{Z}_q[x]/\Phi_1 \Phi_n$ ,  $S_q : \mathbb{Z}_q[x]/\Phi_n$ , and  $S_p : \mathbb{Z}_p[x]/\Phi_n$ . Parameter p is fixed to 3 in all parameter sets of NTRU. Thus, polynomials in  $S_p$  are in ternary form, i.e., have their coefficients in  $\{-1, 0, 1\}$ . In this paper, for NTRU, we use the notation  $S_p$  and  $S_3$  interchangeably. Coefficients of polynomials in  $R_q$ and  $S_q$  have bit-widths of  $\epsilon_q = \log_2 q$  and those of polynomials in  $S_p$  have bit-widths of  $\epsilon_p = \lceil \log_2 p \rceil$ .

In NTRU-HRSS, polynomial f, which is a part of the secret key, is required to have non-negative correlation property,  $\sum_i f_i f_{i+1} \ge 0$ . In NTRU-HPS, polynomial m in  $S_p$ has the fixed-weight property, consisting of d/2 coefficients equal to 1 and d/2 coefficients equal to -1, with d = q/8 - 2. Having the fixed-weight property of m ensures that the ciphertext  $c \equiv 0 \pmod{(q, \Phi_1)}$  in NTRU-HPS. In NTRU-HRSS, in order to achieve the same property of c, m is lifted from  $S_3$  to  $R_q$  by the map  $m \mapsto \Phi_1 \cdot S_3(m/\Phi_1)$ .

**Pseudocode**. The key generation, encryption and decryption of the PKE scheme of NTRU are shown in Algorithms 4, 6 and 7 in Appendix A, respectively [18]. The IND-CCA2 NTRU KEM in Algorithms 5, 8 and 9 in Appendix A, is based on the Saito-Xagawa-Yamakawa variant of the NTRU-HRSS KEM, with improvements that eliminate re-encryption during decapsulation. In the reference implementation of NTRU, the Sample function performs ternary sampling on random input, which requires kilobytes of random data per each operation of key generation or encapsulation. We chose to deviate from the reference implementation by using only 32-byte random input data and expanding it using SHAKE128. Sample generates polynomials in ternary form, which may have either an arbitrary or a fixed weight and/or non-negative correlation property.

During key generation, two polynomial inversions are performed in  $S_3 \pmod{(3, \Phi_n)}$ and  $S_q \pmod{(q, \Phi_n)}$ . All coefficients of polynomials modulo q or p are packed together by unpack\_ $\epsilon_q$  and unpack\_ $\epsilon_p$ . Thus, they must be unpacked before being used in any operation. The Lift function lifts polynomial in  $S_3$  to  $R_q$ . The most critical operation is polynomial multiplication in  $R_q \pmod{(q, (x^n - 1))}$ . Other multiplication operations in  $S_3$  or  $S_q$  can be performed by doing multiplication in  $R_q$ , followed by modulo  $(3, \Phi_n)$  or  $(q, \Phi_n)$ , respectively. During decryption, the ciphertext c is checked to determine if  $c \equiv 0$ (mod  $(q, \Phi_1)$ ). As described in the specification [18], if c is unpacked by unpack\_ $\epsilon_q$ , we only need to check whether the unused bits of the final byte of c are all zeros. r and m are also needed to be checked if they are in the plaintext space, which means their coefficients are in the ternary form, and for NTRU-HPS, m must have the correct fixed weight.

### 3.2.2 CRYSTALS-Kyber

**Polynomial Multiplication.** A basic operation of CRYSTALS-Kyber is the multiplication of two polynomials. In Kyber the polynomials are elements of  $R_q = \mathbb{Z}_q[X]/\langle X^n + 1 \rangle$ .

Thus, for all security levels, polynomials are of the same degree n = 256, and their coefficients are members of the base prime field  $\mathbb{Z}_q$ , where q = 3329. However, a different number of polynomials is required for each security level. These polynomials are treated as a vector. The size of this vector is specified using the parameter k. k is 2, 3, and 4 for security levels 1, 3, and 5, respectively. Secret noise polynomials are sampled from a Centered Binomial Distribution (CBD), where  $\eta$  is either 2 or 3.

An efficient method for polynomial multiplication in  $R_q$  is through the use of the Number-Theoretic Transform (NTT) [25] which is a generalization of the Discrete Fourier Transform (DFT) to the finite ring  $\mathbb{Z}_q$ . In Rounds 2 and 3 of the NIST PQC standardization process, Kyber uses n = 256 and  $q = 3329 = 13 \cdot 2^8 + 1$  where  $2n \nmid q - 1 = 13 \cdot 2^8$ . To make efficient NTT multiplication possible, a new definition of NTT was provided, which transforms a polynomial of degree 256 to a polynomial of degree 128 made up of degree one polynomials as its coefficients.

$$\hat{f}_k = f \mod (X^2 - \zeta^{(2k+1)})$$

(1)

where  $\zeta = 17$  is the first primitive 256-th root of unity modulo q.

In other words  $\hat{f}$  consists of 128 polynomials of degree one:

$$\hat{f}_k = f \mod (X^2 - \zeta^{(2k+1)}) = \hat{f}_{2k} + \hat{f}_{2k+1}X$$

(2)

The sequence of 128 coefficient pairs of degree 1 polynomials can be viewed as a polynomial of degree 256, and then the NTT transform can be expressed separately for the odd and even coefficients:

Point-wise multiplication consists of 128 basic products  $\hat{f} \cdot \hat{g} \mod X^2 - \zeta^{(2i+1)}$ :

$$\hat{h}_{2i} + \hat{h}_{2i+1}X = (\hat{f}_{2i} + \hat{f}_{2i+1}X)(\hat{g}_{2i} + \hat{g}_{2i+1}X) = \left(\hat{f}_{2i}\hat{g}_{2i} + \zeta^{(2i+1)}\hat{f}_{2i+1}\hat{g}_{2i+1}\right) + \left(\hat{f}_{2i}\hat{g}_{2i+1} + \hat{f}_{2i+1}\hat{g}_{2i}\right)X$$

(3)

**Pseudocode**. Pseudocode of the Kyber CPAPKE Key Generation, Encryption, and Decryption are given in algorithms 10, 11, and 12 in Appendix B, respectively. Kyber CCA KEM schemes are built upon the CPAPKE operations, multiple hashing operations, and the FO transformation to achieve the IND-CCA2 security. The detailed algorithms of the Kyber CCAKEM Key Generation, Encapsulation, and Decapsulation are shown in algorithms 13, 14 and 15 in Appendix B.

#### 3.2.3 Saber

A distinctive feature of Saber is that rounding operations are used to avoid the noise addition step and reduce the amount of randomness required. Additionally, by using only moduli that are powers of 2, modular reduction does not require any hardware resources and rejection sampling is eliminated.

**Definitions and Parameters.** Saber involves operations on matrices and vectors of polynomials over the quotient rings  $R_q : \mathbb{Z}_q[x]/(x^n + 1)$  with fixed n = 256. Polynomials in Saber are sampled from the uniform distribution or centered binomial distribution.  $\beta_{\mu}$  denotes a centered binomial distribution with the parameter  $\mu$  and the values of samples in the range  $[-\mu/2; \mu/2]$ . The module dimension l defines the size of vectors and matrices

|                |             |              |              | Encapsulation | Decaps                   | ulation           |                          |  |

|----------------|-------------|--------------|--------------|---------------|--------------------------|-------------------|--------------------------|--|

|                | Small       | Number       | NTT-friendly | One operand   | Number of                | Number of         | Number of                |  |

|                | Coefficient | of           | ring         | in            | "Small" $\times$ "Large" | "Large" × "Large" | "Small" $\times$ "Large" |  |

|                | Range       | coefficients |              | NTT domain    | Polynomial               | Polynomial        | Polynomials              |  |

|                |             |              |              |               | Multiplications          | Multiplications   | Multiplications          |  |

| Kubon 519      | [-33],      |              |              |               | 6                        |                   | 8                        |  |

| Kyber512       | [-22]       | 256          | v            | v             | 0                        |                   | 0                        |  |

| Kyber768       | [-22]       | 230          | 1            | 1             | 12                       | _                 | 15                       |  |

| Kyber1024      | [-22]       |              |              |               | 20                       | _                 | 24                       |  |

| ntruhrss701    | [-11]       | 701          |              |               | 1                        | 1                 | 3                        |  |

| ntruhps2048677 | [-11]       | 677          | N            | N             | 1                        | 1                 | 3                        |  |

| ntruhps4096821 | [-11]       | 821          | 1            |               | 1                        | 1                 | 3                        |  |

| LightSaber-KEM | [-55]       |              |              |               | 6                        | _                 | 8                        |  |

| Saber-KEM      | [-44]       | 256          | N            | N             | 12                       |                   | 15                       |  |

| FireSaber-KEM  | [-33]       | 1            |              |               | 20                       |                   | 24                       |  |

Table 4: Features of algorithms and parameter sets affecting the choice of a multiplier type

of polynomials as  $l \times 1$  and  $l \times l$ , respectively. We denote  $R_q^{l \times l}$  and  $R_q^{l \times 1}$  as a matrix and vector of polynomials in  $R_q$ . The rounding operation includes coefficient-wise addition with a constant factor and is followed by bit shifting.

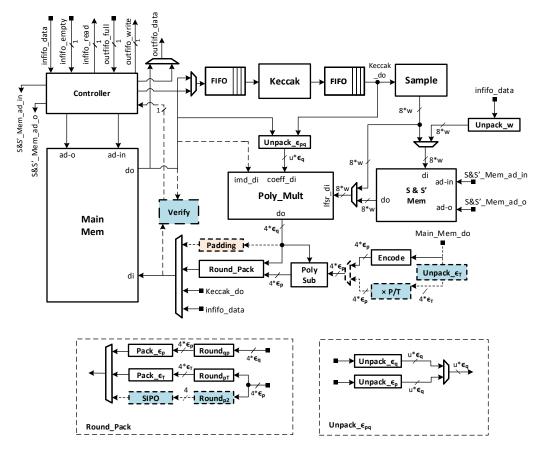

**Pseudocode**. The pseudocode of Saber is shown as Algorithms 16, 17, 18, 20, 19, and 21 in Appendix C. The KEM key generation includes sampling uniformly random matrix A using SHAKE128. Secret vector s is sampled in binomial distribution from the uniformly random output from SHAKE128. The vector product of  $A^T \cdot s$  is rounded and serves as a public vector b in the public key. The secret key includes the public key, hash of the public key, secret vector s, and a pseudo-random byte string z, which is used for implicit rejection in FO transform.

Encapsulation includes encryption with additional hashing. A "small" vector s is generated using sampling from the centered binomial distribution. The ciphertext has two parts. The first part has the rounded product of  $A \cdot s'$ . The second one includes the sum of the inner product of b, s', and the encoded message m. We adopt the optimization in [98] to compute  $b^T \cdot s'$  before  $A \cdot s'$ . Since the generation of s' and A requires the same SHAKE128 function, we would need to finish generating s' before performing  $A \cdot s'$  with the on-the-fly generation of A. The multiplication of  $b^T$  and s' can be performed in parallel with the sampling of s'. The shared secret is derived from the hashes of the public key, message, and ciphertext. Decapsulation involves decryption and re-encryption. During decryption, the secret key is used to compute v, which is used to extract the message. The obtained message is then re-encrypted to check whether the re-encrypted ciphertext is the same as the received one. To save bandwidth, all coefficients of polynomials modulo q or rounded to p or T are packed together by  $pack_e_q$ ,  $pack_e_p$  or  $pack_e_T$ . Thus, they must be unpacked before being used in any operation.

### 3.3 Choice of a Multiplier Type

Major features of investigated algorithms and their parameter sets affecting the choice of a multiplier type are summarized in Table 4.

All four candidates involve multiplication of a polynomial with so-called "small" coefficients, belonging to the range listed in the second column of Table 4, by a polynomial with "large" coefficients, in the range [0..q-1], where q is given in Table 3. Out of four major multiplier types introduced at the end of Section 2, only the Schoolbook multiplier can take full advantage of the feature that "small" coefficients have significantly fewer bits than "large" coefficients. This multiplier has a very regular structure and, in each clock cycle, allows the multiplication of u coefficients of one operand by all coefficients of the second operand. The parameter u is an unrolling factor, typically set to 1, 2, 4, etc. Consequently, the execution time of this multiplier is approximately equal to n/u clock cycles, and its area in LUTs is proportional to n. Since "small" coefficients have from 2 to 4 bits, multiplication by them can be accomplished using ANDs, shifts, and additions. These operations can be efficiently implemented using LUTs and a special fast carry logic of Xilinx FPGAs,

without the need for DSP units. Consequently, all polynomial multiplications in Saber and all-but-one multiplications in NTRU can be efficiently implemented using the Schoolbook multiplier. The disadvantage is a relatively large area, even for the smallest value of the unrolling factor u=1.

An NTT-based multiplier has much smaller area, independent of n, and the execution time proportional to  $n \cdot lg_2(n)$ . They can be sped up using a small number of DSP units. As a result, it is practical to instantiate several such multipliers within the same design without reaching the area threshold. The improvement in execution time depends on data dependencies and the relative speed of units producing inputs to the multipliers. An additional speed-up can be accomplished by defining and/or storing some inputs in the NTT domain. This way, the conversion from the regular to NTT domain may be skipped for one operand. Among the investigated algorithms, only Kyber is defined this way. NTT-based multipliers do not offer any advantage in terms of execution time for the case when one operand has small coefficients. They also impose specific requirements on the dependence between the number of coefficients in each operand, n and the modulus q. If these dependencies do not hold, NTT may still be possible, but it requires extra computations, increasing the multiplier's area and possibly complicating control. Taking all these features into account, an NTT-based multiplier is an obvious choice only for CRYSTALS-Kyber.

As shown in Table 4, NTRU-HPS and NTRU-HRSS are the only investigated candidates that require multiplying two polynomials with "large" coefficients. Values of n and q do not fulfill the requirements of NTT. None of the operands is stored in the NTT domain. As a result, the use of the Toom-Cook multiplier appears to be the best choice. These multipliers have an area smaller than the Schoolbook and larger than NTT types. They can be sped up using a relatively moderate number of DSP units. Consequently, they appear to be the natural choice for the implementation of the "large" by "large" polynomial multiplication in the decapsulation operation of NTRU-HPS and NTRU-HRSS.

# 4 Design and Benchmarking Methodology

As stated in the Introduction, we follow the best understood and commonly trusted RTL methodology. The designers of each implementation worked very closely with each other to ensure a consistent approach to all optimizations. Our designs started when no pure hardware implementations of CRYSTALS-Kyber, NTRU, or Saber were reported in the literature yet. All major designs decisions were made independently of those made in related concurrent projects described in [95], [94], [87], and [98]. All code was developed from scratch without using any library components or any parts of other groups' designs. Consequently, our designs are fully portable, well-documented, and easy to improve and maintain.

All modules common for multiple algorithms, such as the SHA-3/SHAKE unit, were reused. The designs for NTRU and Saber are encoded using VHDL. The design for CRYSTALS-Kyber is encoded using Chisel [6]. We believe that in the RTL methodology, the choice of a hardware description language has a negligible effect on the obtained results. Functional verification of the hardware description language (HDL) code has been performed by comparing simulation results with precomputed outputs generated by a reference software implementation.

On top of this well-known and trusted design methodology, we define a quite straightforward benchmarking methodology. The primary goal is fairness, not a novelty.

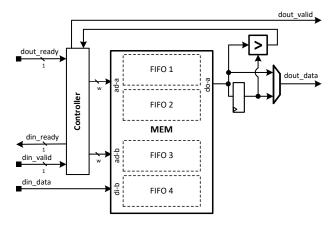

All our hardware implementations assume the use of the FIFO interface defined in [27]. This interface is similar to the interface of the AXI4-Stream Protocol [4].

In terms of functionality of designed units, several options are possible: 1) separate units for encapsulation, decapsulation, and key generation; 2) one unit supporting encapsulation, decapsulation, and key generation, with resource sharing; 3) one unit supporting encapsulation and decapsulation and the second unit responsible for key generation; 4) one unit (on the server-side) supporting key generation and decapsulation, and the second unit (on the client-side) supporting encapsulation. None of these assumptions meet the requirements of all applications. In this paper, we assume Scenario 1). However, whenever possible, we also report results for Scenario 2).

Similarly, there are two major assumptions regarding support for multiple parameter sets: 1. choice among parameters sets at the time of synthesis; 2. choice among parameters sets at run time. The advantage of Approach 1) is the ability to determine the minimum possible resource utilization separately for each security level. Approach 2) demonstrates the flexibility of hardware implementation. However, it will likely require a larger amount of resources than the implementation supporting the highest security level. In this paper, we adopted Approach 1.

One public key and one secret key are assumed to be loaded to the hardware unit before the start of encapsulation and decapsulation, respectively. Thus, the latency of these operations does not include the time required to load the respective keys.

The primary design goal is speed. The speed is characterized using two primary metrics: a) the minimum latency in time units and b) the maximum number of operations per second. These two metrics are related. However, any particular application may have independent requirements in terms of their values. For example, real-time applications, such as secure communication between two autonomous vehicles, may have very strict requirements regarding the time required to establish secure communication and thus the total time required for encapsulation and decapsulation. At the same time, the required number of operations per second may be very small and thus not limiting. On the other hand, a high-traffic server may have to handle thousands of secret key establishments per second. Simultaneously, the time allowed for each individual transaction (and thus the latency of decapsulation) may be quite large.

Taking into account that specific thresholds depend strongly on an application and the state of technology, no specific values are assumed in this benchmarking effort. Instead, we assume that both decreasing latency and increasing the number of operations per second are worthy goals as they will broaden the range of applications that can use a new PQC standard at a given stage of technology. For simplicity, we assume, in agreement with most of the literature, that each design processes only one set of inputs (keys, ciphertexts, random bits) at a time. As a result, the number of operations per second becomes a direct inverse of latency in time units. One, however, should keep in mind an important difference between them: duplicating a design doubles the number of operations per second, but it does not change the latency.

When choosing between multiple potential solutions during the design-space exploration, we give priority to the designs that minimize latency and thus maximize the number of operations per second. However, the parallelization is pursued only until it gives a substantial gain in speed as compared to the area increase in LUTs. Considering that speed and area can be traded one for another, we perform space exploration, using the best available approximations of the execution time in clock cycles and resource utilization in LUTs, DSP units, and BRAMs. Afterward, we choose to include in the speed rankings the implementations of each candidate that are the closest to each other in terms of resource utilization.

For our target platforms, we chose representative devices of two different FPGA / FPGA SoC families: Artix-7 and Zynq UltraScale+. Specifically, we choose the largest devices of both families supported by free versions of Xilinx tools. For each device, we assume that its highest speed grade is used. These assumptions led us to choosing a) Artix-7 XC7A200T-3, with 134,600 LUTs, 365 BRAMs, and 740 DSP units, and Zynq UltraScale+ ZU7EV-3, with 230,400 LUTs, 312 BRAMs, 96 Ultra BRAMs, and 1,728 DSP units. Based on the previous work, summarized in Section 2, these devices are sufficient

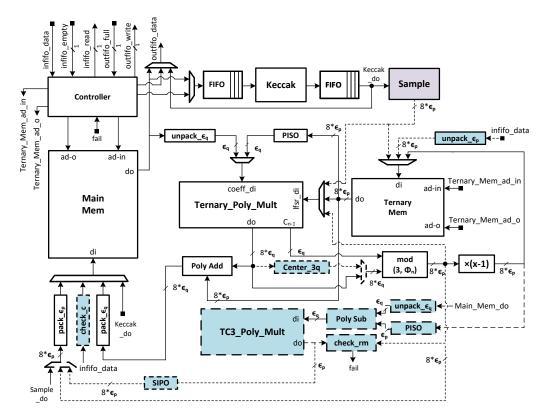

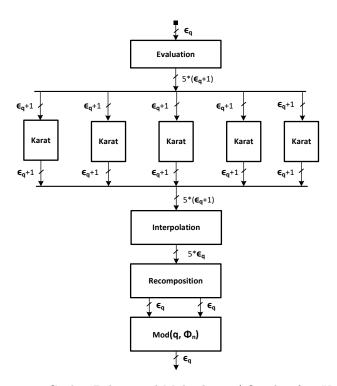

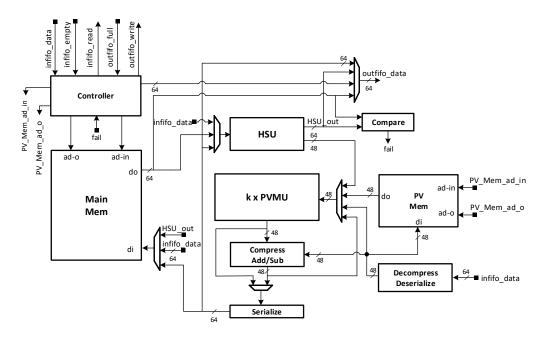

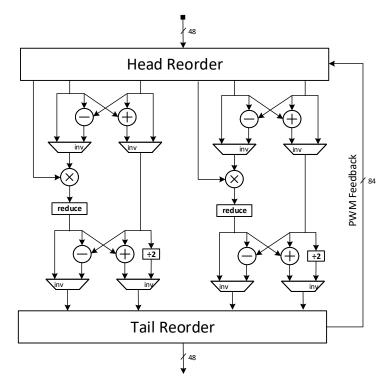

Figure 3: Top-level block diagrams of the Encapsulation and Decapsulation modules of NTRU. The purple, blue modules are used only in Encapsulation and Decapsulation, respectively.

for a vast majority of designs reported to date. Out of their resources, the number of LUTs is the most limiting. The use of BRAMs and DSP units is typically negligible. Therefore, for the purpose of design-space exploration, we use the number of LUTs as a measure of the circuit *Area*. The maximum clock frequency is determined using binary search. Only final results obtained after placing and routing are reported.

# 5 Hardware Designs

### 5.1 NTRU

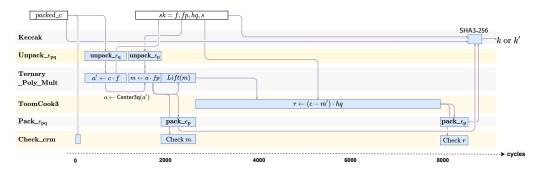

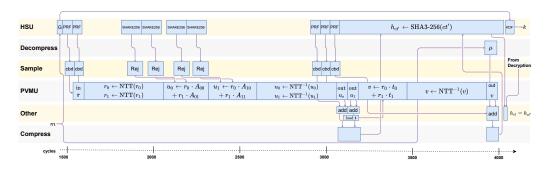

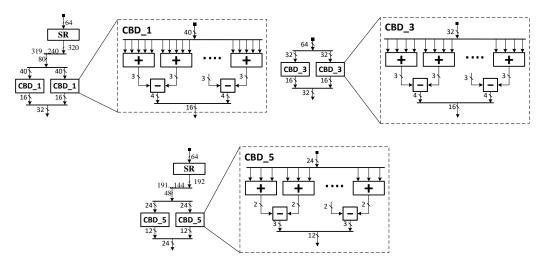

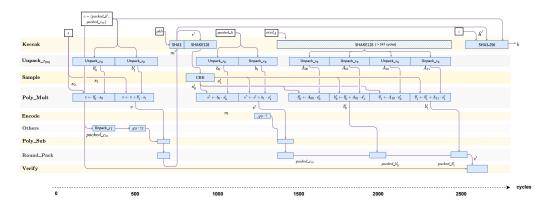

The top-level diagram of NTRU is shown in Fig. 3. The scheduling of major operations during encapsulation, decapsulation, and key generation is illustrated in Figs 4, 5, and 6, respectively.

### 5.1.1 Ternary Sampling

For NTRU-HRSS, the generation of f and g is performed in  $S_3$  during key generation. Random bytes coming from SHAKE128 are reduced modulo 3 to obtain the ternary coefficients stored in a first-in, first-out (FIFO) unit. The sum of products of consecutive coefficients  $s = \sum_i f_i f_{i+1}$  is computed at the same time. After finishing generating all coefficients, if s < 0, coefficients at even indices are signed-flipped before being transferred to the next computational stage. Thus, the non-negative correlation properties of f and g are satisfied. g is later multiplied by x - 1, which can be carried out trivially during

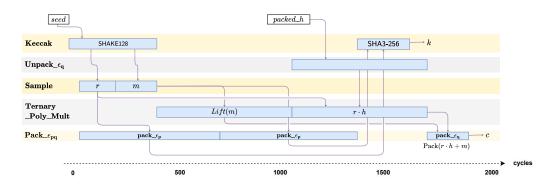

Figure 4: Operations Scheduling for Encapsulation of NTRU-HRSS.

Figure 5: Operations Scheduling for Decapsulation of NTRU-HRSS.

Figure 6: Operations Scheduling for Key Generation of NTRU-HRSS.

the transfer. During encryption, r and m do not have either the non-negative correlation property or fixed-weight. They can be computed by simply reducing random data modulo 3.

For NTRU-HPS, f and r have arbitrary weight and can be sampled in a straightforward manner. However, m and g have fixed weight and are sampled by creating a random permutation of a list with a fixed number of values -1, 0 and 1. One can simply perform Fisher-Yates shuffle to have a random non-biased permutation of such a list. However, Fisher-Yates shuffle is not constant-time and creates a risk of potential timing attacks. Given that, we adopt a constant-time merge sorting approach for the permutation. The merge-sort module requires n random elements. Each element includes 30 random bits concatenated with "01" for the first w/2 elements, "10" for the next d/2 elements, and "00" for the rest. To get a 30-bit block, a 64-bit input is passed through a PISO, to be divided into two 32-bit blocks. Each 32-bit block is then processed using a buffer register and a

Figure 7: FIFO-based merge sort module for NTRUHPS2048677.

Figure 8: One stage of a FIFO-based merge sort module implemented using dual-port memory.

variable shifter to get a 30-bit block. The leftover bits are stored in the buffer register to be concatenated with the subsequent output of PISO. After sorting, the upper 30 bits are discarded, and the lower 2 bits are converted from  $\{0, 1, 2\}$  to  $\{0, 1, -1\}$ .

Related works: Wang et al. [91] proposed a fully pipelined constant-time merge sort module to generate random permutation in the Key Generation operation of Classic McEliece. To sort a random list of n elements, the module needs  $log_2(n)$  iterations, where each step requires O(n) comparison operations. Therefore, the total cycle count is approximately equal to  $nlog_2(n)$  cycles. Marotzke [66] implemented an iterative Batcher's merge exchange sort module for a very similar sampling function in the Streamlined NTRU Prime. Its operation also have asymptotic complexity of  $O(nlog_2(n))$ .

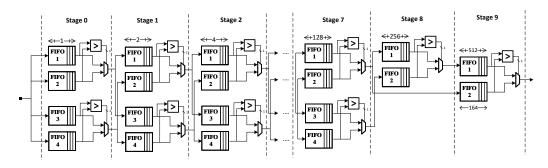

To speed up this operation, we use a merge-sort module consisting of  $log_2(n)$  cascaded Sort Stages to sort the random sequences. The FIFO-based merge-sort module for NTRU-HPS677 is shown in Fig. 7. The inputs to each Sort Stage are two sorted lists, and the output is a sorted list of double input length, including all elements from the two input lists. Each input list is stored in a separate segment of memory. While the lower stages can be implemented by registers, the higher stages are implemented in dual-port memory. This approach can reduce the number of LUTs and FFs used to construct the large FIFO in higher stages at the cost of a small number of BRAMs. The internal structure of a Sort Stage is shown in Fig 8. By making use of the dual-port memory, the controller in each stage can write out the sorted list to the next stage and receive other input lists from the previous stage at the same time. By pipelining the operation of multiple Sort Stages, we can achieve a highly optimized latency for sorting. Our merge-sort module requires nclock cycles for reading n elements, roughly n cycles for sorting, and another n cycles to

|                                                 | Freq.                                                 | LUT       | $\mathbf{FF}$ | BRAM | DSP | Cycles     |  |  |  |

|-------------------------------------------------|-------------------------------------------------------|-----------|---------------|------|-----|------------|--|--|--|

| NTRUPRime: $n = 761, w = 32$ , Zynq Ultrascale+ |                                                       |           |               |      |     |            |  |  |  |

| Batcher's Merge Exchange Sort [66]              | 279                                                   | 231       | 87            | 1.0  | 0   | 49,400     |  |  |  |

| FIFO-based Merge Sort                           | 250                                                   | $1,\!441$ | 940           | 3.5  | 0   | 2,762      |  |  |  |

| ClassicMcEliece: $n =$                          | ClassicMcEliece: $n = 8192, w = 45, Zynq Ultrascale+$ |           |               |      |     |            |  |  |  |

| 4x Pipelined Merge Sort [91]                    | 250                                                   | 583       | 411           | 20.0 | 0   | 147,505    |  |  |  |

| FIFO-based Merge Sort                           | 250                                                   | 2,533     | 1,589         | 33.0 | 0   | $26,\!646$ |  |  |  |

Table 5: Implementation Results of the FIFO-based Merge Sort module and comparison with related works.

write out a sorted sequence. In particular, sampling m or g takes 2,678 and 3,343 cycles for NTRU-HPS677 and NTRU-HPS821, respectively.

The comparison of our FIFO-based merge sort module with previous work is shown in Table 5. We synthesize our module with the parameters used in [66] and [91]. Since the code of [91] is open-source, we can synthesize their merge-sort module targeting the same platform, Zynq Ultrascale+, and obtain results. Our FIFO-based merge sort module outperforms the previous designs by roughly an order of magnitude, excluding the time to load input and unload output. Although the increase in resource utilization is significant, it is still a quite compact design, suitable for high-speed applications that require random constant-time permutation.

### 5.1.2 Polynomial Multiplication

In all previous work on hardware implementations of NTRU, the polynomial multipliers always exploited the property of small ternary coefficients. The schoolbook multiplication has quadratic-complexity but enables simple, parallel, easy-to-parameterize, and very fast architecture for polynomial multiplication in NTRU. In [68], an efficient architecture based on the Toom-Cook algorithm is proposed in a Software/Hardware codesign platform. Toom-Cook 4-way was applied to divide polynomial multiplication of 256 coefficients into seven multiplications with 64 coefficients. These seven multiplications are run in parallel using seven schoolbook polynomial multipliers.

In the AVX2 implementation of the NTRU submission package [73], a multi-layer Toom-Cook and Karatsuba are used to speed up the multiplication. In the recent work [19], an NTT-based polynomial multiplication is proposed, which outperforms the Toom-Cook method. However, the NTT-based polynomial multiplication was also applied to only multiplication with ternary polynomials. Therefore, it is not applied to speed up the key generation and the final multiplication in decryption, which does not have any input polynomial in ternary form.

**Toom-Cook Polynomial Multiplier.** In this work, for multiplication without involving ternary polynomial, we implement a Toom-Cook 3-way polynomial multiplier, which splits an *n*-coefficient polynomial multiplication into five multiplications with n/3 coefficients. The five multiplications are performed in parallel using five Odd-Even Karatsuba multipliers. Our improvements over [68] include:

- Our implementation supports splitting input polynomials into three smaller polynomials before the Evaluation step. The Toom-Cook core in [68] relies on software to do this operation.

- Using the Odd-Even Karatsuba method significantly improves the latency of the multiplication step.

- Our core supports Recomposition, which has the output polynomial in the ring  $R_q$ .

Figure 9: Toom-Cook 3 Polynomial Multiplier w/ Overlap-free Karatsuba.

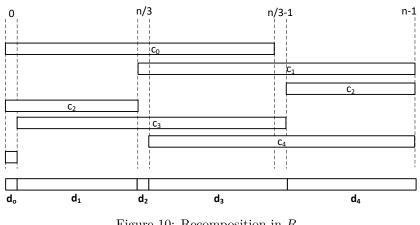

Figure 10: Recomposition in  $R_q$ .

In [68], 5 output polynomials are transferred to software and are then recomposed into a single polynomial.

Toom-Cook and Karatsuba are multiplication algorithms that have better asymptotic complexity compared to the schoolbook method. Toom-Cook k-way is a generalization of Karatsuba with k = 2. Both algorithms generally follow five steps: splitting, evaluation, pointwise multiplication, interpolation, and recomposition. The input polynomials are split into 2k - 1 polynomials with n/k coefficients. These polynomials are then evaluated at 2k - 1 points. The evaluated polynomials are multiplied in the pointwise-multiplication steps. The results are interpolated as an opposite of the evaluation step. The output polynomials of the interpolation step are finally recomposed into the final product.

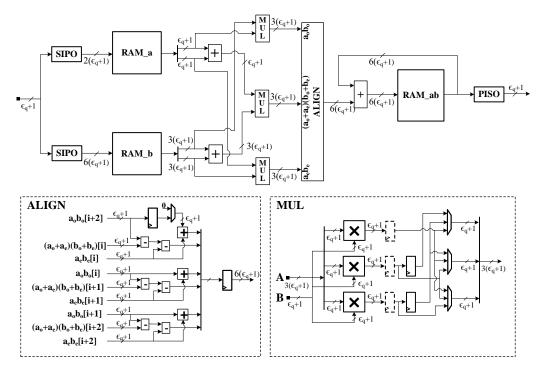

The top-level diagram of the Toom-Cook 3-way module is shown in Fig. 9. Toom-

Figure 11: Overlap-free Karatsuba polynomial multiplier.

Cook 3-way splits input polynomial A(x) into three polynomial  $a_0, a_1$  and  $a_2$  such that  $A(y) = a_0 + a_1y + a_2y$ , where  $y = \lceil n/3 \rceil$ .  $a_0, a_1$  and  $a_2$  are then evaluated at five points  $\{0, 1, -1, 2 \text{ and } \infty\}$ . The pointwise multiplications are performed by Odd-Even Karatsuba modules. We adopt the optimal sequence for evaluation and interpolation in the Toom-Cook 3-way from Bodrato et al. [16]. We would like to highlight that during evaluation, there is a division by 2, which becomes a one-bit shift and causes a one-bit loss of precision. Therefore, the pointwise multiplication and interpolation steps require one extra bit for each coefficient.

After interpolation steps, we have 5 output polynomials  $c_0, c_1, \ldots c_4$  with 2n/3 coefficients needed to be recomposed and reduced modulo  $x^n - 1$  in the ring  $R_q$ . Fig. 10 shows the positions of polynomials  $c_0, c_1 \ldots c_4$  in the final product polynomial d modulo  $x^n - 1$ . Since the recomposition module receives five coefficients with the same index from  $c_0$  to  $c_4$ , we need two registers  $d_0, d_2$  and three shift registers of the size  $\lfloor n/3 \rfloor - 1$ . For example,  $d_0$  will be initialized with the coefficient from  $c_0$  at the cycle 0, then it is added to a coefficient from  $c_2$  in the cycle  $\lfloor n/3 \rfloor - 1$  and lastly added with the last coefficient from  $c_4$  in the cycle  $\lfloor 2n/3 \rfloor - 1$ .

The overlap-free Karatsuba splits input polynomial A(x) into two polynomials  $a_0$ and  $a_1$  such that  $A(y) = a_0 + a_1 y$  where y = x. It means that  $a_0$  consists of all even coefficients of A(x); meanwhile,  $a_1$  consists of all odd coefficients of A(x). The overlap-free Karatsuba scheme enables a more efficient alignment of product coefficients compared to the classic Karatsuba scheme. The diagram of our overlap-free Karatsuba module is shown in Fig. 11. Two polynomials are stored in RAM\_a and RAM\_b. The multiplication between two coefficients from RAM\_a and RAM\_b would normally cost 12 integer multipliers. However, this number is reduced to 9 multipliers thanks to the Karatsuba algorithm. The latency of this module can be calculated as follows:

Pointwise-Multiplication Latency =  $\left(\frac{n}{6\times 3} + 1\right) \times \left(\frac{n}{6} + 1\right)$

Figure 12:  $S_2/S_3$  Inversion Module

interpolation, respectively. Each splitting/evaluation or recomposition/interpolation takes  $\lceil 2n/3 \rceil$  cycles. Our Toom-Cook multiplier finishes one polynomial multiplication in  $R_q$  or  $S_q$  in 5507, 5098 and 7274 cycles for n = 701, 677 and 821, respectively.

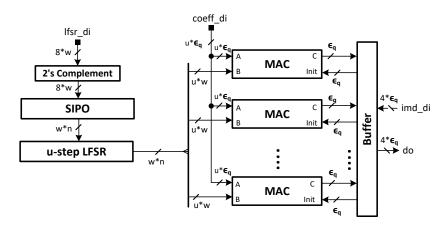

**Ternary Polynomial Multiplier.** For multiplications involving polynomial in the ternary form  $\{-1, 0, 1\}$ , we use the constant-time LFSR-based polynomial multiplier, proposed in [27], which has the latency of n clock cycles. By loading the ternary polynomial with coefficients in  $\{-1, 0, 1\}$  to the LFSR, instead of a polynomial with "big" coefficients, we reduce the number of flip-flops required to realize this LFSR by a factor of four. We also shorten the time required to load a polynomial into the LFSR, since eight 2-bit coefficients can be loaded in a single clock cycle. All integer multiplication-and-accumulation operations between coefficients of two operands and one product polynomials are reduced to addition, pass-through, or subtraction. The LFSR is initialized to a polynomial with ternary coefficients. Let us denote the initial state of this LFSR as a(x). In each subsequent iteration, the output from LFSR contains the value  $a(x) \cdot x^i \mod x^n - 1$ . In a single clock cycle, a simple multiplication by x, namely  $a(x) \cdot x^{i+1} \mod x^n - 1 = a(x) \cdot x^i \cdot x \mod x^n - 1$ , is performed.

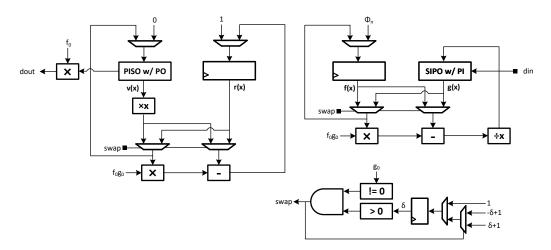

### 5.1.3 Inversion in $S_3$ and $R_q$

The inverse of polynomials in  $R_q$  and  $S_3$  plays an important role in key generation. We need to compute  $f_p$ , which is an inverse of f in  $S_3$  for the secret key. Computation of  $v_1$ , which is an inverse of  $v_0$  in  $S_q$ , must be completed before any later operations could proceed.

Inversion in  $S_3$ : Inversion in  $S_3$  is done using the constant-time extended Greatest Common Divisor (GCD) unit proposed in [15]. The top-level diagram of our S3\_inverse module is shown in Fig. 12. At first, g(x) is initialized with an input polynomial in reverse order. f(x), r(x) and v(x) are initialized with  $\Phi_n$ , 1 and 0 respectively. The module runs in exactly 2(n-1) cycles. All coefficients of four polynomials are updated simultaneously during each iteration according to the value of  $\delta$  and  $g_0$ . All operations, including addition, subtraction, and multiplication, are reduced modulo 3. Multiply and divide by x are performed by simple bit shifting. Lastly, the inverse of input polynomial is  $f_0 \times v(x)$ . We note that the inverse polynomials are also stored in the reverse order. Our module also supports inversion in  $S_2$ , which is used in inversion in  $S_q$ . We compare our results for NTRU-HPS821 with n = 821 with the Reciprocal in R/3 module in the implementation of Streamlined NTRU Prime in [66]. We have shown that the extended GCD can be

Table 6: Implementation results of the Extended GCD module and comparison with related work for Streamlined NTRU Prime in Zynq Ultrascale+ platform.

|                                | Freq. | LUT       | $\mathbf{FF}$ | BRAM | DSP | Cycles    |

|--------------------------------|-------|-----------|---------------|------|-----|-----------|

| Extended GCD w/ $n = 761$ [66] | 271   | 518       | 216           | 0    | 0   | 1,168,899 |

| Extended GCD w/ $n = 821$      | 250   | $8,\!534$ | $5,\!479$     | 0    | 0   | $1,\!846$ |

### **Algorithm 1** Polynomial Inversion in $S_q$ [50]

**Input:** Polynomial a in  $S_q$  **Output:** Polynomial b in  $S_q$  such that  $a \cdot b = 1 \mod (q, \Phi_n)$ 1:  $v_0 \leftarrow a^{-1} \mod (2, \Phi_n)$ 2:  $i \leftarrow 1$ 3: while i < logq do 4:  $v_0 \leftarrow v_0 \cdot (2 - a \cdot v_0)$ 5:  $i \leftarrow 2i$ 6: end while 7:  $b \leftarrow v_0$

#### Algorithm 2 Lift in NTRU-HRSS [50]

**Input:** Polynomial v in  $S_3$ **Output:** Polynomial  $b = \Phi_1((v/\Phi_1) \mod (3, \Phi_n)) \mod (q, \Phi_1 \Phi_n)$

1:  $z = [1/\Phi_1] \mod (3, \Phi_n) = \sum_{i=0}^{n-2} (1-i) \cdot x^i \pmod{3}$ 2:  $a = vz \mod (q, \Phi_1 \Phi_n)$ 3: for i = 0 to n - 1 do 4:  $a_i = a_i - a_{n-1} \pmod{3} \qquad \triangleright a = v/\Phi_1 \mod (3, \Phi_n)$ 5: end for 6:  $b_0 = a_{n-1} - a_0 \pmod{q}$ 7: for i = 1 to n - 1 do 8:  $b_i = a_{i-1} - a_i \pmod{q} \qquad \triangleright b = \Phi_1((v/\Phi_1) \mod (3, \Phi_n)) \mod (q, \Phi_1 \Phi_n)$ 9: end for

implemented in an unrolled fashion, achieving highly optimized latency.

Inversion in  $R_q$ : To compute the inverse of h in  $S_q$ , we perform  $h^{-1} \mod (2, \Phi_n)$  and then apply a variant of the Newton iteration in  $R_q$  to obtain  $h_q \equiv h^{-1} \mod (q, \Phi_n)$ . The pseudocode of inversion in  $R_q$  is given in Algorithm 1. A similar approach is presented in [50], which finds an inverse mod  $(2, \Phi_n)$  using  $h^{-1} \equiv h^{2^{n-1}-2} \mod (2, \Phi_n)$ . Given that squaring operation in  $\mathbb{Z}_2[x]$  is particularly very efficient in software, this approach is suitable for software implementation. In our case, we can re-use our S3\_inverse module to compute inversion in  $S_2$ . All arithmetic operations are now reduced modulo 2 instead of 3 as in inversion in  $S_3$ . Operations from lines 3 to 6 in Algorithm 1 are equivalent to 8 polynomial multiplications, which are performed by the Toom-Cook multiplier. Due to the long latency of the polynomial multiplication, inversion in  $R_q$  is the most time-consuming operation in Key Generation of NTRU.

#### 5.1.4 Lift function

Lift function in NTRU-HPS applies a simple map to ternary coefficients of m, converting  $\{0, 1, -1\}$  to  $\{0, 1, q - 1\}$ . This can done on-the-fly by sign extending all the coefficients from  $\epsilon_p = 3$  bits to  $\epsilon_q$  bits.

In NTRU-HRSS, the Lift function maps m from  $S_3$  to  $R_q$  by doing  $m \mapsto \Phi_1 \cdot S_3(m/\Phi_1)$ . An efficient implementation of Lift is shown in Algorithm 2. As shown in the pseudocode, Lift function can be performed by one multiplication with  $z = 1/\Phi_n$  then followed by reduction modulo  $(3, \Phi_n)$  and lastly multiplied by  $\Phi_1$ . Since z is a constant ternary polynomial, it is stored in the memory and the multiplication can be performed by the Ternary\_Poly\_Mult in n cycles. Reduction modulo  $(3, \Phi_n)$  and multiplication by  $\Phi_1 = x - 1$  can be performed on-the-fly while transferring result back to the memory.

#### 5.1.5 Operations scheduling

In Figs 4, 5, and 6, we show the scheduling of major operations for NTRU-HRSS. Similar schedulings are also applied to NTRU-HPS with two significant differences as follows:

- Lift(m) in NTRU-HPS is simpler compared to NTRU-HRSS. The function is executed on-the-fly while storing m to the memory without occupying the Ternary Polynomial Multiplier.

- Sampling m in Encapsulation and g in Key Generation take much longer time since they require constant-time sort-based sampling.

Almost all pack and unpack operations are hidden by overlapping them with Polynomial Multiplications and/or Sampling. In Decapsulation, the valid checks of r and m are executed in parallel with packing them. The majority of the execution time of Decapsulation is taken by the "large"  $\times$  "large" polynomial multiplication. Meanwhile in Key Generation, the polynomial inversion in  $R_q$  takes up to 90% of total latency.

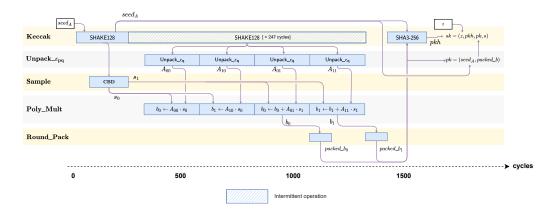

### 5.2 CRYSTALS-Kyber

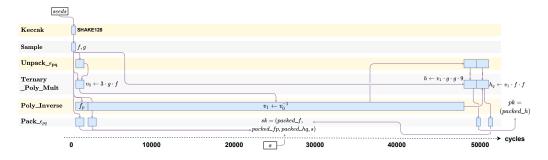

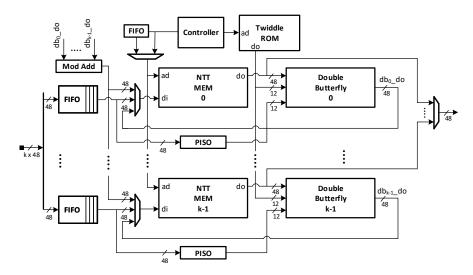

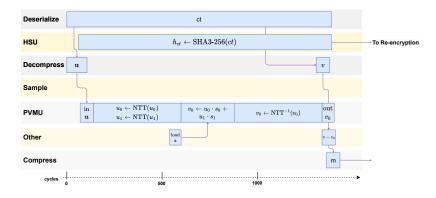

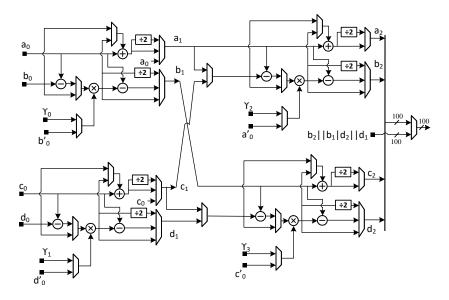

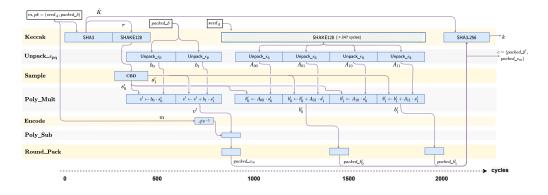

The proposed hardware architecture for Round 3 Kyber supports the following variants and operations: a) CPA-PKE: Key Generation, Encryption, and Decryption, and b) CCA-KEM: Key Generation, Encapsulation, and Decapsulation. The top-level unit is shown in Fig. 13. The hardware is implemented in Chisel hardware design language [6][52] and incorporates state-of-the-art techniques for optimizing speed and minimizing the resource overhead. The scheduling of operations and units for security level 1 in Decapsulation is shown in Figs 15 and 16.

#### 5.2.1 Polynomial NTT and Multiplication Unit

The Polynomial-Vector Multiplication Unit (PVMU) can perform forward and inverse NTT operations concurrently on up to k polynomials, where k is the security level parameter. This unit also performs polynomial point-wise multiplication (PWM) and accumulation to compute vector-vector and matrix-vector multiplications. The top-level block diagram of PVMU is shown in Fig. 14. At the security level k, the PVMU module consists of k DoubleButterfly pipelines and k memory banks (NTT RAM), each with a single read port and a single write port and datawidth of  $4 \times 12$  bits (4 coefficients). On the input path, k FIFOs exist, which allow receiving up to k polynomials while a previous operation underway and the main memory bank port are busy.

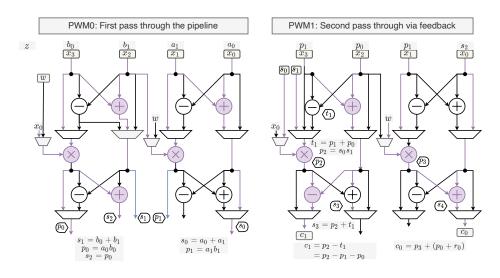

A DoubleButterfly pipeline consists of two merged parallel configurable radix-2 butterflies, which can operate in three modes of operation: DIT (Decimation in Time) NTT, DIF (Decimation in Frequency) iNTT (inverse NTT), and point-wise multiplication (PWM). During the NTT/iNTT operations, each DoubleButterfly pipeline carries out two radix-2 butterfly operations in parallel for odd and even coefficients. The structure of a Double-Butterfly pipeline is shown in Fig. 17. The butterfly datapath is deeply pipelined (up to 12 stages) to achieve good operating frequency.

Figure 13: Block diagram of the Kyber top-level datapath

In each butterfly pipeline, a reordering of the input coefficients may be required, depending on the butterfly operation (DIF/DIT/PWM). This is performed by the Head Reorder unit at the input of the butterfly pipeline. A corresponding reordering at the end of the butterfly pipeline is performed by the Tail Reorder unit. During DIF/DIT operations, these reorder units operate as multi-path delay commutators (MDC), [96], not only enabling an efficient memory access scheme similar to [84], but also ensuring correct ordering of the stored coefficients and avoiding the need for any subsequent reordering steps.

The inverse NTT operation involves scaling all coefficients by  $256^{-1}$ . In many software and hardware implementations, the scaling step is performed in a separate step requiring 256 additional field multiplications for each polynomial. By performing a division by 2 (mod q) at each layer of inverse NTT, the scaling step can be entirely avoided. This observation was also used by Zhang et al. [97]. In that implementation, two divide-by-2 hardware units are utilized to scale both outputs of the radix-2 iNTT butterfly. In our implementation, we use a single divide-by-2 unit for each butterfly, and the other output of each butterfly is scaled by using a scaled copy of the twiddle factors during the inverse transform.

The twiddle factors are stored in a single ROM shared by all butterfly pipelines and are mapped to BRAM-based memory during the FPGA synthesis.

Kyber's point-wise multiplication of polynomials a and b (both in NTT domain) is performed on base degree 1 polynomials in the form of  $a_{2i} + a_{2i+1}X$  and  $b_{2i} + b_{2i+1}X$ . The resulting polynomial  $c = a \cdot b$  is calculated using the following formula:

$$c_{2i} + c_{2i+1}X = (a_{2i} + a_{2i+1}X)(b_{2i} + b_{2i+1}X) \mod X^2 - \zeta_i$$

which results to:

$$\begin{cases} c_{2i} = a_{2i}b_{2i} + a_{2i+1}b_{2i+1}\zeta_i \\ c_{2i+1} = a_{2i}b_{2i+1} + a_{2i+1}b_{2i} \end{cases}$$

The straightforward formulation requires 5 modular multiplications for producing a pair of coefficients. As demonstrated by Xing et al. in [95], by using the Karatsuba method, only 4 modular multiplications is required:

Figure 14: Block diagram of the Kyber Polynomial-Vector Multiplication Unit (PVMU)

Figure 15: Kyber scheduling of operations for the Decryption stage of Decapsulation at the security level 1

$$\begin{cases} c_{2i} = a_{2i}b_{2i} + a_{2i+1}b_{2i+1}\zeta_i \\ c_{2i+1} = (a_{2i} + a_{2i+1})(b_{2i} + b_{2i+1}) - a_{2i}b_{2i} - a_{2i+1}b_{2i+1} \end{cases}$$

With slight adjustments to the double-butterfly structure and careful scheduling of the pipelines, the same resources are used to perform the point-wise multiplication. The scheduling of the DoubleButterfly pipeline for point-wise multiplication is shown in Figure 18. A feedback loop walks coefficients twice through the pipeline to perform 4 modular multiplications and the required addition and subtractions. The two passes through the pipeline are interleaved in such a way to allow full utilization of the multiplier and reduction units of both butterflies in each cycle and requiring only 128 cycles to perform a full polynomial point-wise multiplication (depending on the subsequent operation, a maximum of 21 additional cycles may be required to flush the pipeline).

#### 5.2.2 Barrett reduction with support for division

Coefficients of polynomials are elements of a finite field (or ring)  $\mathbf{Z}_q$ , where q is a small constant modulus (less than 20 bits). In Kyber q is a prime. This choice requires a modular reduction step after most arithmetic operations to keep the bit width of the

Figure 16: Kyber scheduling of operations for the Re-encryption stage of Decapsulation at the security level 1

Algorithm 3 Optimized Barrett Modular Reduction and Division

**Require:**  $0 \le u \le (q-1)^2$ **Ensure:**  $r = u \mod q, r \in [0,q)$ ▷ remainder **Ensure:**  $u = d.q + r \mod q, d \in [0,q)$ ▷ quotient **Generation Time:** Find optimal values for  $\alpha$  and  $\beta$  such that: 1. Only a single conditional subtraction is required 2. Multiplication with the constant  $\mu$  has minimal hardware complexity. For Kyber Round 3:  $q := 3329, \ n := \lceil \log_2(q) \rceil = 12, \ \alpha := 12, \ \beta := -2, \ \mu := \lfloor \frac{2^{n+\alpha}}{q} \rfloor = 5039$ function BARRETTREDUCE(u)  $u_h \leftarrow u \gg (n+\beta)$  $\triangleright$  discard  $n + \beta$  least-significant bits  $d \leftarrow (\mu \cdot u_h) \gg (\alpha - \beta)$  $\triangleright$  discard  $\alpha - \beta$  least-significant bits  $r \leftarrow u - d \cdot q$ if  $r \ge q$  then  $\triangleright$  conditional subtraction  $r \leftarrow r - q$  $d \leftarrow d + 1$ end if end function

data bounded. Variants of Barrett [11], Montgomery [69], K-RED [65], and SAMS2 [62] reduction algorithms have been used in software and hardware implementations of R-LWE schemes.

We use an optimized variant of the Barrett reduction algorithm shown in Algorithm 3. As shown by Knezevic et al. [58], by careful selection of parameters  $\alpha$  and  $\beta$ , only one level of conditional subtraction will be required. The hardware generator code creates optimized single constant multipliers (SCM) based on shift-adder trees and ternary adders based on [60].

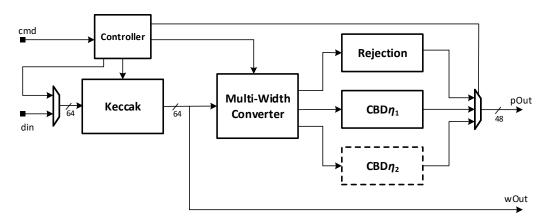

### 5.2.3 Hash and Sampling Unit