# Randomness Optimization for Gadget Compositions in Higher-Order Masking

Jakob Feldtkeller<sup>1</sup>, David Knichel<sup>1</sup>, Pascal Sasdrich<sup>1</sup>, Amir Moradi<sup>2</sup> and Tim Güneysu<sup>1,3</sup>

<sup>1</sup> Ruhr University Bochum, Horst Görtz Institute for IT Security, Bochum, Germany firstname.lastname@rub.de <sup>2</sup> University of Cologne. Institute for Computer Science. Germany

firstname@uni-koeln.de

<sup>3</sup> DFKI, Bremen, Germany

**Abstract.** Physical characteristics of electronic devices, leaking secret and sensitive information to an adversary with physical access, pose a long-known threat to cryptographic hardware implementations. Among a variety of proposed countermeasures against such Side-Channel Analysis attacks, *masking* has emerged as a promising, but often costly, candidate. Furthermore, the manual realization of masked implementations has proven error-prone and often introduces flaws, possibly resulting in insecure circuits. In the context of automatic masking, a new line of research emerged, aiming to replace each physical gate with a secure gadget that fulfills well-defined properties, guaranteeing security when interconnected to a large circuit. Unfortunately, those gadgets introduce a significant amount of additional overhead into the design, in terms of area, latency, and randomness requirements.

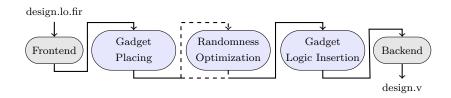

In this work, we present a novel approach to reduce the demands for randomness in such gadget-composed circuits by reusing randomness across gadgets while maintaining security in the probing adversary model. To this end, we embedded the corresponding optimization passes into an Electronic Design Automation toolchain, able to construct, optimize, and implement masked circuits, starting from an unprotected design. As such, our security-aware optimization offers an additional building block for existing or new Electronic Design Automation frameworks, where security is considered a first-class design constraint.

**Keywords:** Masking · Probing Security · Strong Non-Interference · Probe Isolating Non-Interference · Security-Aware Optimization · Security-Aware EDA

# 1 Introduction

In 1999, Paul Kocher introduced Differential Power Analysis (DPA) as a powerful threat to the security of cryptographic hardware and devices [KJJ99]. In the aftermath, this remarkable work sparked interest and innovation in entirely new branches of research dealing with Side-Channel Analysis (SCA), showing that the observation of physical characteristics of an electronic device, such as timing behavior [Koc96], instantaneous power consumption [KJJ99], electromagnetic (EM) radiations [GMO01], or temperature and heat dissipation [HS13], can reveal secret and sensitive information to any observer and adversary with physical access. Over the last two decades, researchers, among other things, pursued research covering the development of novel *side-channel attacks*, the enhancement of *analysis techniques*, and the design and implementation of *effective countermeasures*.

In this context, masking (based on the concepts of secret sharing) has been established as the most promising candidate for protection against SCA due to its theoretical and sound security foundations [CJRR99]. Consequently, many different schemes and variants have been proposed and implemented in hardware over the last years [ISW03, Tri03, NRS11, RBN<sup>+</sup>15, GMK17, GM18], of which not a few have been shown to be insecure due to design flaws or inaccurate assumptions, e.g., [MMSS19]. Even today, the design and implementation of secure hardware is still a mostly manual and error-prone process, requiring long-standing expertise in hardware design and security. Consequently, recent research focuses on novel approaches and concepts facilitating the implementation of security in hardware through accurate models and consolidated security notions.

Security and Composability Notions. In the context of hardware masking, the simple and abstract Ishai-Sahai-Wagner (ISW) t-probing adversary and security model [ISW03] provides strong theoretical foundations and clear formal models for adversaries and physical execution environments of modern hardware devices. In its basic form, the t-probing model grants an adversary access to up to t intermediate values of an ideal circuit during the processing of sensitive information. Extended with unconsidered and unintentional physical effects, including glitches [MPG05, MS06], transitions [CGP<sup>+</sup>12, BGG<sup>+</sup>14], and couplings [CBG<sup>+</sup>17], the robust t-probing model [FGP<sup>+</sup>18] provides an accurate verification model to reason about the security of masked digital logic circuits. Unfortunately, the design and implementation of masked circuits is a non-trivial problem, as complexity increases with the design size, and the combination and composition of masked circuits may result in insecure constructions.

Accordingly, modern approaches endeavor to extend security to larger circuits through the composition of atomic masked circuits, often denoted as *gadgets*, guaranteeing security in the *t*-probing model when interconnected. To this end, novel security notions, such as Non-Interference (NI) [BBD<sup>+</sup>15], Strong Non-Interference (SNI) [BBD<sup>+</sup>16], and Probe Isolating Non-Interference (PINI) [CS20], have been proposed recently, defining gadget-contained properties that enable secure composition. Although the security and composability notions assist in the construction and verification of secure circuits, each gadget instantiation comes with additional overhead in terms of *latency increase*, *area occupation*, and *randomness demand*. More specifically, the local overhead for each gadget, introduced through the composability notions, accumulates for the entire circuit and often results in non-optimal solutions.

**Security-Aware Construction and Optimization.** Even beyond performance and area overhead, the composed constructions are often more secure than strictly required, as composability properties are often maintained even for the combined circuit, although eventually, only security against the *t*-probing adversary is required. For this, modern security-aware Electronic Design Automation (EDA) tools should not only assist designers in the construction of secure circuits through combining and composing masked gadgets but also provide ways and means to optimize the final construction in terms of area or performance while maintaining the desired level of security. This becomes even more important and pronounced for higher-order masking, as the performance and area penalty usually grows exponentially in the security order.

While there are already some initial concepts and tools to design and verify composed circuits [BGR18, CGLS21, KMMS22], all of the given tools maintain gadget barriers and boundaries without further optimization and improvement of the final masked circuits. Consequently, this leads to the question, whether dissolving gadget barriers and boundaries can help to share resources and, hence, decrease the overhead introduced through conservative security notions.

**Our Contributions.** Given these observations and research questions, we present a novel approach to optimize and reduce the final randomness consumption and requirements

of masked circuits created through the composition of securely masked gadgets. Set within this context, we attempt to use a holistic view of the composed circuit to identify clusters of gadgets that can share and re-use randomness while maintaining an appropriate level of security under the t-probing adversary model. More precisely, our approach is designed and well-suited for higher-order masking (i.e.,  $t \ge 2$ ) using state-of-the-art gadget constructions created under the SNI and PINI composability notions. Embedded into an efficient EDA flow, using the Multi-Level Intermediate Representation (MLIR) framework as a fundamental basis, we present novel optimization strategies and passes that allow constructing, optimizing, and implementing masked circuits, starting from an unprotected design. Depending on the context and application scenario, our optimization strategies allow reduction of the randomness demand of a masked AES-128 by up to 13% when utilizing state-of-the-art PINI gadgets and up to 94% when using SNI gadgets.

**Outline.** We first provide some core concepts and definitions used throughout the paper in Section 2. Then, in the main part of this paper, we introduce our optimization techniques for both SNI and PINI compositions in Section 3 and Section 4, respectively. In Section 5 we describe the implementation and integration of our optimization passes into an EDA toolchain for construction and optimization of masked circuits while we evaluate the performance and assess the practical security of our randomness reduction techniques in Section 6. Section 7 discusses existing and related work as well as possible extensions for the future, before we conclude in Section 8.

# 2 Preliminaries

In the following, we introduce necessary notations and recall the most important definitions from the literature required throughout the paper.

### 2.1 Notations

In Table 1, we provide a summary of important notation and variables used throughout this work. Further, calligraphic fonts are used to denote sets while we use superscripts to indicate the index of a gadget within a set, while subscripts are used for indices of shares and random bits.

### 2.2 Modeling and Masking Circuits

Any logic circuit realizing a Boolean function  $\mathsf{F} : \mathbb{F}_2^u \mapsto \mathbb{F}_2^w$ , can be abstracted as a graph [ISW03, FGP<sup>+</sup>18]. More formally, any stateful and deterministic circuit  $\mathsf{C}$  can be modeled as a Directed Acyclic Graph (DAG)  $\mathsf{D}_{\mathsf{C}} = \{\mathcal{V}, \mathcal{E}\}$ , with vertices  $v \in \mathcal{V}$  describing either combinatorial gates or synchronization elements, i.e., registers, and edges  $e \in \mathcal{E}$  describing wires carrying elements drawn from  $\mathbb{F}_2$ .

**Boolean Masking.** Boolean masking splits a secret  $x \in \mathbb{F}_2^u$  into d > 1 independent and uniformly distributed shares  $x_i \in \mathbb{F}_2^u, 0 \le i < d$ , such that  $x = \bigoplus_{i=0}^{d-1} x_i$ . For this, each  $x_i$  for  $0 \le i < d-1$  is usually sampled from a uniform random distribution over  $\mathbb{F}_2^u$ , while the remaining share is derived as  $x_{d-1} = \bigoplus_{i=0}^{d-2} x_i \oplus x$ .

**Encoded Circuit Model.** The secure computation of y = C(x) can be formally defined through a *circuit compiler* [AIS18] consisting of three algorithms, i.e., COMPILE, ENCODE, and DECODE.

|                                                                                                                | Table 1: Summary of notation and variables.                                                    |

|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| n                                                                                                              | Number of gadgets                                                                              |

| t                                                                                                              | Security order                                                                                 |

| d                                                                                                              | Number of shares                                                                               |

| m                                                                                                              | Number of random elements required for one gadget                                              |

| $\hat{m}$                                                                                                      | Number of random elements overall                                                              |

| $\mathcal{R}^k$                                                                                                | Ordered set of random elements used in the $k$ 'th gadget                                      |

| $r_i$                                                                                                          | <i>i</i> 'th randomness element of overall randomness                                          |

| $r_i^k$                                                                                                        | i'th randomness element usd in the $k$ 'th gadget                                              |

| $r^k_i \\ r^k_{i,j}$                                                                                           | Randomness used to mask products between share index $i$ and $j$ in the $k\mathrm{'th}$ gadget |

| Т                                                                                                              | (Simplified) computation tree                                                                  |

| $\mathcal{V}$                                                                                                  | Set of vertices in T                                                                           |

| ${\mathcal E}$                                                                                                 | Set of edges in T, i.e., shares of intermediate values                                         |

| $\bar{\mathcal{E}}$                                                                                            | Set of unshared edges in T, i.e., intermediate values                                          |

| $\bar{E}^{i,j}$                                                                                                | Unshared edge in $T$ between $i \in \mathcal{V}$ and $j \in \mathcal{V}$                       |

| $egin{array}{l} \mathcal{V} \ \mathcal{E} \ ar{\mathcal{E}} \ ar{\mathcal{E}}^{i,j} \ ar{P}^{i,j} \end{array}$ | Unshared path in T between $i \in \mathcal{V}$ and $j \in \mathcal{V}$                         |

| $a^k$                                                                                                          | Left-hand-side input to the $k$ 'th gadget                                                     |

| $b^k$                                                                                                          | Right-hand-side input to the $k$ 'th gadget                                                    |

| $c^k$                                                                                                          | Output the k'th gadget                                                                         |

| $a_i^k$                                                                                                        | <i>i</i> 'th share of the left-hand-side input to the $k$ 'th gadget                           |

| $b_i^{\check{k}}$                                                                                              | i'th share of the right-hand-side input to the $k$ 'th gadget                                  |

| $a_i^k\ b_i^k\ c_i^k$                                                                                          | i'th share of the output of the $k$ 'th gadget                                                 |

| -                                                                                                              |                                                                                                |

Table 1: Summary of notation and variables.

While COMPILE is a deterministic algorithm which takes a circuit C as input and outputs a masked circuit<sup>1</sup>  $\tilde{C}$ , the ENCODE algorithm is probabilistic and transforms a secret x into its masked representation  $\tilde{x}$ . DECODE is again a deterministic algorithm converting a masked representation  $\tilde{y}$  into the plain value y. Eventually, the secure computation of y from x is given as the concatenated execution of ENCODE, followed by  $\tilde{C}$ , terminated with DECODE.

#### 2.3 ISW *t*-Probing Model

In the literature, the ISW t-probing model [ISW03] has proven to be an accurate adversary model enabling the formal verification of masked circuits on the one hand, and construction of masking schemes on the other.

**Probing on Ideal Circuits.** In the standard *t*-probing model, an adversary is granted the ability to probe up to *t* arbitrary wires of a masked circuit  $\tilde{C}$ , without having access to any information related to ENCODE and DECODE. However, assuming an ideal circuit, probes are restricted to only observe the current value of the wire. Then, *t*-probing security is achieved if an adversary is not able to retrieve any information on the secret given up to *t* probes.

**Probing in the Presence of Glitches.** Since ideal circuits do not capture physical defects in hardware implementations, i.e., *glitches, transitions*, and *couplings*, the *t*-probing model was extended to the *robust probing model* by Faust et al. [FGP<sup>+</sup>18]. In particular, glitches are a well-known source of information leakage in logic circuits due to unintentional activities caused by different signal and switching delays. To accurately capture these effects, in the glitch-extended robust *t*-probing model, each adversarial probe is extended to capture all values up to the last synchronization point (register or primary input),

<sup>&</sup>lt;sup>1</sup>Throughout this work, we always assume a Boolean masking scheme.

contributing to the observed value. For this, each standard probe is substituted by a glitch-extend variant, and security is defined as the adversary not learning any information on the secret given up to t glitch-extended probes.

**Probe Simulation and Propagation.** According to Cassiers and Standaert [CS20], a probe propagates into another wire if the value on this wire is needed to perfectly simulate the distribution of the probed value, where *perfect simulation* is defined by Definition 1. This intuitively means that probes spread backwards through a circuit until they are stopped by some randomness refreshing. Hence, probes can capture information leakage of other wires contributing to the computation of the observed value.

**Definition 1** (Perfect Probe Simulation). Let  $\mathcal{P}$  be a set of probes placed on a masked circuit. Then  $\mathcal{P}$  is *perfectly simulatable* by a set  $\mathcal{X}$  of input shares iff there exist a probabilistic polynomial time (ppt) simulator *sim*, such that for any values of the inputs to the masked circuit, the probability distribution over  $\mathcal{P}$  and  $sim(\mathcal{X})$  are equal.

### 2.4 Composability Notions

As formal verification and construction of masking schemes are increasingly challenging for higher security orders and larger circuits, different composability notions have been established. Each of them aimed at enabling the construction of small, masked sub-circuits, commonly denoted as *gadgets*, which provable lead to security in the (robust) *t*-probing model when composed to a larger circuit.

For this, all common composability notions restrict probe propagation for single gadgets, allowing to argue about probe propagation and security in composed circuits. More precisely, a single (extended) probe placed inside a gadget is restricted to propagate only to a limited set of input shares of the respective gadget, where the concrete limitation is specific to the composability notion.

*t*-Non-Interference. The notion of NI [BBD<sup>+</sup>15], as defined in Definition 2, restricts probe propagation without differentiating between internal and output probes. It implies *t*-probing security but has proven to be insufficient to guarantee composability.

**Definition 2** (Non-Interference). A masked circuit  $\tilde{C}$  is *t*-NI iff for every probe set  $\mathcal{P}$  containing  $t' \leq t$  probes, there exists a set  $\mathcal{X}$  containing at most t' shares per input, such that  $\mathcal{P}$  can be perfectly simulated by  $\mathcal{X}$ .

**Strong Non-Interference.** For the SNI composability notion [BBD<sup>+</sup>16], an adversary is allowed to learn partial information on shared inputs when placing probes on wires inside the gadget. However, for every probe positioned on an output of the gadget, the adversary is not allowed to learn any additional input shares. More formally, t-SNI is defined according to Definition 3.

**Definition 3** (*t*-Strong Non-Interference). A single-output, masked circuit C is *t*-SNI iff for every probe set  $\mathcal{P}$  containing  $t_1$  internal probes and  $t_2$  output probes, such that  $t_1 + t_2 \leq t$ , there exists a set  $\mathcal{X}$  containing at most  $t_1$  shares per input, such that  $\mathcal{P}$  can be perfectly simulated by  $\mathcal{X}$ .

As this definition is limited to single-output gadgets, SNI was extended to Multiple-Output Strong Non-Interference (MO-SNI) by Cassiers and Standaert [CS20] to cover multiple-output gadgets as well.

**Definition 4** (Multiple-Output Strong Non-Interference). A masked circuit C provides t-MO-SNI iff for every probe set  $\mathcal{P}$  containing  $t_1$  internal probes and up to  $t_2$  probes on each output, such that  $t_1 + t_2 \leq t$ , there exists a set  $\mathcal{X}$  containing at most  $t_1$  shares per input, such that  $\mathcal{P}$  can be perfectly simulated by  $\mathcal{X}$ .

**Probe Isolating Non-Interference.** Since trivial (i.e., share-wise) implementations of linear operations are not SNI, Cassiers and Standaert introduce the notion of *t*-PINI [CS20], enabling trivial implementations by restricting probes to only propagate within a single-share domain. More formally, *t*-PINI is defined according to Definition 5.

**Definition 5** (Probe Isolating Non-Interference). Let  $\mathcal{P}$  be a set of  $t_1$  internal probes and some probes on outputs. Further, let  $\mathcal{I}_{\mathcal{O}}$  be the set of share indices assigned to these output probes in  $\mathcal{P}$ , with  $|\mathcal{I}_{\mathcal{O}}| = t_2$  and  $t_1 + t_2 \leq t$ . A masked circuit  $\tilde{C}$  is *t*-PINI iff for every  $\mathcal{P}$ , there exists a set of indices  $\mathcal{I}_{\mathcal{I}}$  with  $|\mathcal{I}_{\mathcal{I}}| \leq t_1$ , such that the distribution observed by  $\mathcal{P}$  can be perfectly simulated by input shares corresponding to share domains drawn from  $\mathcal{I} = \mathcal{I}_{\mathcal{I}} \cup \mathcal{I}_{\mathcal{O}}$ .

### 2.5 Restricted Composability Notions

In the context of this work, we introduce a variant of MO-SNI and PINI, which restricts the number of adversarial probes placed on gadget outputs more strictly. More precisely, our variants only allow  $t_2$  adversarial probes placed on all outputs instead of  $t_2$  probes placed at each output.

**Definition 6** (*t*-Restricted Multiple-Output Strong Non-Interference). A masked circuit  $\tilde{C}$  provides *t*-Restricted Multiple-Output Strong Non-Interference (RMO-SNI) iff for every probe set  $\mathcal{P}$  containing  $t_1$  internal probes and  $t_2$  output probes, such that  $t_1 + t_2 \leq t$ , there exists a set  $\mathcal{X}$  containing at most  $t_1$  shares per input, such that  $\mathcal{P}$  can be perfectly simulated by  $\mathcal{X}$ .

**Definition 7** (*t*-Restricted Probe Isolating Non-Interference). Let  $\mathcal{P}$  be a set of  $t_1$  internal probes and  $t_2$  output probes with  $t_1 + t_2 \leq t$ . Further, let  $\mathcal{I}_{\mathcal{O}}$  be the set of share indices assigned to the output probes. A masked circuit  $\tilde{\mathsf{C}}$  provides *t*-Restricted Probe Isolating Non-Interference (R-PINI) iff for every  $\mathcal{P}$ , there exists a set of indices  $\mathcal{I}_{\mathcal{I}}$  with  $|\mathcal{I}_{\mathcal{I}}| \leq t_1$ , such that the distribution observed by  $\mathcal{P}$  can be perfectly simulated by input shares corresponding to share domains drawn from  $\mathcal{I} = \mathcal{I}_{\mathcal{I}} \cup \mathcal{I}_{\mathcal{O}}$ .

Obviously, these notions do not enable arbitrary compositions but require special care and construction, ensuring that a set of probes placed onto the composed circuit does not propagate into more than t output probes of a gadget. These definitions can be used to make statements about probing security and secure composition even when the full composability notions do not hold after optimization. We show how those notions can be ensured and leveraged to optimize the randomness used across gadget boundaries.

Further, we highlight that both RMO-SNI and R-PINI imply NI respectively. The reason is that both RMO-SNI and R-PINI restrict the adversary to at most t' < t probes in total, which are simulated with at most t' shares of each input. This is exactly the definition of NI. In other words, if an R-PINI or RMO-SNI simulator exists for  $\mathcal{P}$ , then the NI simulator simply runs the same simulation on the same simulation set.

### 2.6 Computation Tree

In order to perform our cross-gadget optimizations, it is necessary to argue about connections between gadgets. For this, we define further abstractions of our circuit model, such that vertices in the graph represents gadgets, and each edge represent one share of an intermediate value. Please note, there always exist t + 1 parallel edges in a masked computation tree.

**Definition 8** (Computation Tree). We define the *computation tree* of a masked circuit  $\tilde{C}$  as a Directed Acyclic Multigraph (DAMG)  $T = (\mathcal{V}, \mathcal{E})$ , with vertices  $\mathcal{V} = \{G^0, G^1, \ldots, G^{n-1}\}$ representing all gadgets from  $\tilde{C}$  in addition to primary inputs and outputs, while edges  $\mathcal{E} = \{E_{\ell}^{i,j} \mid i \in \mathcal{V}, j \in \mathcal{V}, \ell \leq t\}$  represents all wires between those gadgets in  $\tilde{C}$ . Further, following Cassiers et al. [CS20], a *simplified computation tree* is constructed according to Definition 9. In essence, the transformation removes the connection between inputs and outputs of SNI gadgets.

**Definition 9** (Simplified Computation Tree). A simplified computation tree is defined as a computation tree where all SNI gadgets G are divided into two separate parts  $G_{in}$ and  $G_{out}$ , such that the inputs of G are connected to  $G_{in}$ , and  $G_{out}$  is connected to the outputs of G. Further,  $G_{in}$  has no outputs and  $G_{out}$  has no inputs.

Since each edge in the (simplified) computation tree represents a wire in the circuit, each share belonging to one intermediate value is represented with its own edge. For situations where we only care about the existence of an edge connecting two vertices, we say an *unshared edge* is the set of edges belonging to the same unshared intermediate value. Using this, we can define an *unshared path* as a collection of connected unshared edges. Hence, for an unshared path, we only consider the existence of a connection between two gadgets and not the possible routes over different shares. However, we emphasize that this is just a formal concept with no impact on the underlying physical implementation.

**Definition 10** (Unshared Path). Let  $\mathsf{T} = (\mathcal{V}, \mathcal{E})$  be a (simplified) computation tree. Further, let  $\bar{\mathcal{E}}$  be a set of *unshared edges* such that  $\bar{E}^{i,j} \in \bar{\mathcal{E}}$  iff  $E_{\ell}^{i,j} \in \mathcal{E}$  for some  $\ell$ . Then we define an *unshared path*  $\bar{P}^{a,b}$  in  $\mathsf{T}$  as a sequence of connected edges  $\{\bar{E}^{a,i_1}, \bar{E}^{i_1,i_2}, \ldots, \bar{E}^{j_1,j_2}, \bar{E}^{j_2,b}\}$ , with  $\bar{E}^{i,j} \in \bar{\mathcal{E}}$ .

# 3 Randomness Reduction for DOM-Gadget Composition

We first consider gadget compositions based on the notion of SNI. For this, we discuss how to use properties of SNI to cluster multiple gadgets before we show how to reuse randomness within such clusters. In the following, we assume a design composed of NI-addition gadgets and Domain-Oriented Masking (DOM)-multiplication and DOM-refresh gadgets [GMK17] where only the DOM gadgets require fresh randomness.

### 3.1 Clustering DOM Gadgets

Our first goal is to divide the set of DOM multiplication and DOM refresh gadgets into different clusters, such that we can reuse randomness within each cluster, i.e., two gadgets belonging to the same cluster may share some randomness.

When reusing randomness among different gadgets, it has to be ensured that refreshing one value does not actually result in the removal of already introduced randomness. Hence, values dependent on the same randomness need always to be separate from each other.

In addition, sharing and reusing randomness among different gadgets potentially causes inter-gadget leakage, i.e., a probe placed within one gadget can capture leakage of additional input shares through the leakage of other gadgets. While the SNI property of a gadget generally restricts the amount of information that is leaked and captured by a single probe (i.e., the number of input shares), it does not constrain the source of information leakage (i.e., the share index). In consequence, to prevent critical cross-gadget leakage from revealing additional input shares, gadgets that can share and reuse the same randomness must have inputs independent of each other.

Further, we observe that the essential property of SNI gadgets is a share refreshing that removes any dependency between the output and the gadget inputs. Basically, this property is the foundation for SNI composition, introduced by Barthe et al. [BBD<sup>+</sup>16], and was generally shown by Belaüd et al. [BGR18]. However, this property allows not only to cluster parallel gadgets from different paths of the computation tree due to independent inputs, but also gadgets that lie in different paths within the *simplified* computation tree (which can be at the same path in the computation tree).

(b) Example assignments for Definition 13

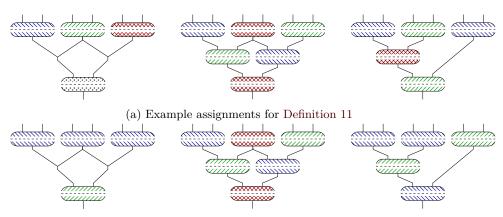

Figure 1: Example assignments in different clusters, where nodes represent DOM gadgets (according to a simplified computation tree) and NI gadgets are left out for brevity (at intersections or at edges). Matching colors and fill patterns resemble gadgets belonging to the same cluster and all edges represent unshared edges.

**Definition 11** (Clustering of DOM Gadgets). Let  $\mathsf{T} = (\mathcal{V}, \mathcal{E})$  be a simplified computation tree of vertices  $\mathcal{V} = \{G^0, G^1, \ldots, G^{n-1}\}$  and edges  $\mathcal{E} = \{E_{\ell}^{i,j} \mid i \in \mathcal{V}, j \in \mathcal{V}, \ell \leq t\}$ . A cluster of DOM gadgets is a set  $\mathcal{C} \subseteq \mathcal{V}$  such that:

$$\forall \{G^i, G^j\} \in \mathcal{C}^2, i \neq j \mid \nexists G \in \mathcal{V} : \exists \bar{P}^{G, G^i} \land \exists \bar{P}^{G, G^j} \tag{1}$$

$$\forall \{G^i, G^j\} \in \mathcal{C}^2, i \neq j \mid \nexists \bar{P}^{G^i, G^j} \tag{2}$$

$$\forall \{G^i, G^j\} \in \mathcal{C}^2, i \neq j \mid \nexists G \in \mathcal{V} : \exists \bar{P}^{G^i, G} \land \exists \bar{P}^{G^j, G} \tag{3}$$

$$\forall G^i \in \mathcal{C}, \forall G^j \in \mathcal{V}, i \neq j \mid \nexists \bar{P}^{G^i, G^j} \lor \exists ! \bar{P}^{G^i, G^j} \tag{4}$$

Here, Property (1) ensures that all inputs to the clusters are independent of each other, as there is no path from one *source* to multiple inputs of the cluster. Property (2) requires that there is no path from an output of the cluster to an input of the same cluster, ensuring the independence of the contained gadgets. Intuitively, those two properties restrict the cross-gadget leakage. Property (3) is symmetric to Property (1) in that it ensures that there is no path from multiple outputs of the cluster to the same *sink* gadget. This property is required to restrict the number of probes that can propagate to the outputs of the cluster. For the same reason, Property (4) restricts the number of paths from one output to all other gadgets to at most one. However, we included this property for completeness only, as it is always true for secure compositions of NI and SNI gadgets. The clustering principle is illustrated in Figure 1a for different scenarios.

We now prove that such a cluster can have at most t (propagated-)probes at outputs of the containing gadgets, meaning that the cluster requires RMO-SNI only, instead of MO-SNI, for probing security. We use Properties (3) and (4) from Definition 11 here, while the other properties are required later to prove Theorem 2.

**Theorem 1.** Let  $\mathsf{T} = (\mathcal{V}, \mathcal{E})$  be a simplified computation tree with gadgets in  $\mathcal{V}$  that are t-NI or t-SNI and let  $\mathcal{C}$  be a cluster according to Definition 11. Further, let  $\mathcal{P}$  be a set of probes on  $\mathcal{V}$  and  $\mathcal{E}$ , with  $|\mathcal{P}| \leq t$ . Then, there are at most t probes at output shares of  $\mathcal{C}$  including probe propagation and glitch extension of probes.

*Proof.* Assume a cluster  $\mathcal{C}$  according to Definition 11 within a simplified computation tree  $\mathsf{T} = (\mathcal{V}, \mathcal{E})$ . We further assume a set of probes  $\mathcal{P}$  on  $\mathcal{V}$  and  $\mathcal{E}$  with  $|\mathcal{P}| \leq t$ . In general,

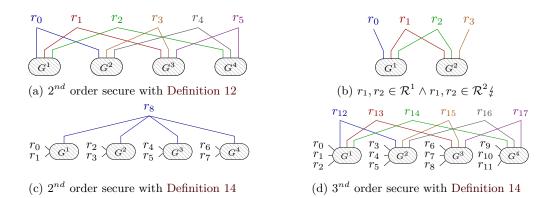

Figure 2: Example of randomness assignment for clusters of DOM gadgets, where (2a) represents a valid assignment. The assignment in (2b) is insecure, as the pair of randomness  $\{r_1, r_2\}$  is used both in  $G^1$  and  $G^2$ . In (2c) and (2d) a secure assignments with gadget unique randomness for  $2^{nd}$  and  $3^{rd}$  order security is shown.

there are two scenarios how the output of a gadget is probed: (1) by directly probing the corresponding signal or (2) by probe propagation after placing a probe on an internal signal (for this proof we consider glitch extension of probes as a form of probe propagation). Assume  $|\mathcal{P}| = t_1 + t_2$  probes, among which  $t_1$  probes are placed directly on outputs of  $\mathcal{C}$ , and  $t_2$  probes elsewhere. It trivially holds that  $t_1 \leq t$ . Due to Properties (3) and (4), there is at most one unshared path from each actual probe to outputs of  $\mathcal{C}$ . Hence, a probe can not duplicate during probe propagation through different paths. In addition, the definition of NI and SNI guarantee that probes can not duplicate within gadgets. Therefore, there are at most  $t_2$  probes capturing the outputs of  $\mathcal{C}$  derived from probe propagation. This means, there are  $t_1 + t_2 \leq t$  probes capturing the outputs of of  $\mathcal{C}$ , which proofs Theorem 1.  $\Box$

**Randomness Assignment for DOM Gadgets.** After clustering gadgets according to Definition 11, the assignment of fresh randomness to gadgets follows a simple rule: Randomness can be reused between gadgets of the same cluster as long as there is no pair of random elements  $\{r_i, r_j\}$  which is used in more than one gadget. In other words, there is no pair of gadgets that share more than one random element. We provide illustrative examples for the correct randomness reuse and an incorrect one in Figure 2a and Figure 2b respectively. Intuitively, this rule ensures that a probe placed in a single gadget can only leak one additional input share of other gadgets through cross-gadget leakage, as there is at most one random element that is reused between two gadgets. Definition 12 captures this rule of correctly reusing randomness for DOM gadgets within a cluster more formally.

**Definition 12** (RMO-SNI-Randomness Assignment). Given a cluster C as defined in Definition 11, for all DOM gadgets  $G^k \in C$  random elements can be assigned arbitrarily to  $G^k$  as long as the following condition holds:

$$\forall k, \forall \{r_i, r_j\} \in \mathcal{R}^k \mid \nexists k' \neq k : \{r_i, r_j\} \in \mathcal{R}^{k'}, \tag{5}$$

where  $r_i$  stands for the *i*-th random element and  $\mathcal{R}^k$  is the set of randomness used for the gadget  $G^k$ .

**Security Proof.** We now prove that this rule ensures t-RMO-SNI for a cluster of DOM gadgets. More precisely, we take the gadget variant of Faust et al. [FGP<sup>+</sup>18], which was made t-SNI by adding an additional register layer at the output. The description of such

Algorithm 1: A single cluster, containing n DOM-multiplication gadgets, with reduced randomness (equal to definition in [FGP<sup>+</sup>18] for n = 1).

1 function clusterDOM( $(a^0, b^0), ..., (a^{n-1}, b^{n-1})$ ): **Require:**  $t \ge 2$ **Require:** All inputs are independent of each other **Require:**  $a^k, b^k \in \mathbb{F}_2^{t+1}$  such that  $a^k: (a_0^k, \dots, a_t^k), b^k: (b_0^k, \dots, b_t^k)$  with  $\sum_j a_j^k = a^k$ and  $\sum_{j} b_{j}^{k} = b^{k}$ // Initialize randomness for k = 0 to n - 1 do 2  $R^{k} = \left\langle r_{0}^{k}, \dots, r_{m-1}^{k} \right\rangle \leftarrow \text{Distribution according to Definition 12}$ 3 4  $q \leftarrow 0$ for i = 0 to t do 5  $\begin{array}{l} \mathbf{for} \ j = i+1 \ to \ t \ \mathbf{do} \\ \\ r_{i,j}^k \leftarrow r_q^k; \ r_{j,i}^k \leftarrow r_q^k \\ \\ q \leftarrow q+1 \end{array}$ 6 7 8 // Compute multiplication gadgets for k = 0 to n - 1 do 9 for i = 0 to t do 10  $w_i^k \leftarrow a_i^k \cdot b_i^k$ 11  $\begin{array}{l} \mathbf{for} \ j = i + 1 \ to \ t \ \mathbf{do} \\ \\ u_{i,j}^k \leftarrow a_i^k \cdot b_j^k + r_{i,j}^k \\ \\ u_{j,i}^k \leftarrow a_j^k \cdot b_i^k + r_{j,i}^k \end{array}$ 12 13 14  $\begin{array}{l} \mathbf{for} \ i=0 \ to \ t \ \mathbf{do} \\ & \begin{bmatrix} s_i^k \leftarrow \mathrm{Reg}[w_i^k] + \sum_{j=0, j \neq i}^t \mathrm{Reg}[u_{i,j}^k] \\ & c_i^k \leftarrow \mathrm{Reg}[s_i^k] \end{array}$ 15 16 17 **Ensures:**  $c^k : (c_0^k, \dots, c_t^k) \in \mathbb{F}_2^{t+1}$  such that  $\sum_j c_j^k = a^k \cdot b^k, \forall k$ return  $c^0, \ldots, c^{n-1}$ 18

a cluster with *n* DOM gadgets is given in Algorithm 1. Please note that we can see the composition of the *n* DOM gadgets, constructing the cluster, as a new gadget for which we prove security. Further, we can restrict the argumentation to multiplication gadgets only, as SNI-refresh gadgets can be trivially constructed by SNI-multiplication gadgets where one input is a constant Boolean sharing of 1, e.g.,  $\langle 1, 0, \ldots, 0 \rangle$  (cf. [BGR18]).

**Theorem 2.** clusterDOM, as defined in Algorithm 1, is t-RMO-SNI secure under the glitch-robust t-probing model.

Proof. Let us denote a set of internal probes  $\mathcal{P}_{\mathcal{I}}$  and a set of output probes  $\mathcal{P}_{\mathcal{O}}$  with  $\mathcal{P}_{\mathcal{I}} \cup \mathcal{P}_{\mathcal{O}} \leq t$ . Without loss of generality, we restrict the probes to only capture  $w_i^k$ ,  $u_{i,j}^k$ ,  $s_i^k$ , and  $c_i^k$  as, due to glitch extension, all other probe positions capture a portion of these probes. In Algorithm 2, we give an algorithm that, given the set of probes  $\mathcal{P}_{\mathcal{I}} \cup \mathcal{P}_{\mathcal{O}}$ , returns a set of input shares  $\mathcal{X}$  required to simulate the probes for the gadget defined in Algorithm 1. In particular, Algorithm 2 returns all inputs such that all required intermediate values can be computed exactly as in Algorithm 1 except for some  $u_{ij}^k$ . We first show that, for all possible probe placements, Algorithm 2 adds at most one share of each input to  $\mathcal{X}$  for each internal probe. Afterwards, we show that the inputs in  $\mathcal{X}$  enable a simulation of the set of probes  $\mathcal{P}_{\mathcal{I}} \cup \mathcal{P}_{\mathcal{O}}$ , as required for t-RMO-SNI.

For some probe placed on  $w_i^k$  it is obvious that Algorithm 2 only adds one share of each input to  $\mathcal{X}$  (i.e.,  $a_i^k, b_i^k$ ). The same is true for a probe on  $s_i^k$  when  $\nexists\{k', x, y, j\}$  such that  $r_{x,y}^{k'} = r_{i,j}^k$  with a probe placed on  $u_{x,y}^{k'}$  or  $s_x^{k'}$ , since then, Line 12 of Algorithm 2 is not

#### Algorithm 2: Input-share chooser for the simulator of ParDOM multiplication.

1 function ShareChooser<sup>clusterDOM</sup> ( $\mathcal{P}_{I} \cup \mathcal{P}_{O}$ ):  $\mathcal{X} \leftarrow \emptyset$  $\mathbf{2}$ for i = 0 to t do 3 for k = 0 to n - 1 do 4 5 6 for j = 0 to  $t, j \neq i$  do if  $u_{ij}^k$  is probed then  $\begin{bmatrix} \mathcal{X} \leftarrow \mathcal{X} \cup \{a_i^k, b_j^k\} \\ \text{if } s_i^k \text{ and at least one value } u_{x,y}^{k'} \text{ or } s_x^{k'} \text{ such that } r_{xy}^{k'} = r_{i,j}^k \text{ is probed then} \\ \begin{bmatrix} \mathcal{X} \leftarrow \mathcal{X} \cup \{b_j^k\} \end{bmatrix}$ 7 8 9 10 11  $\mathbf{12}$ return  $\mathcal{X}$

reached. However, if there is a probe placed on  $s_i^k$  and  $\exists \{k', x, y, j\}$  such that  $r_{x,y}^{k'} = r_{i,j}^k$ and a probe is placed on  $u_{x,y}^{k'}$ , then the set  $\{a_i^k, b_i^k, b_j^k, a_x^{k'}, b_y^{k'}\}$  is added to  $\mathcal{X}$ . Naturally, this adds at most two shares of each input (using two probes) if  $k' \neq k$ . For k' = k, either y = i or y = j, since  $r_{i,j}^k$  is only used at most twice in each internal gadget, and  $r_{i,j}^k = r_{j,i}^k$ . Hence, again, only at most two shares of each input are added to  $\mathcal{X}$  (using two probes). Otherwise, if a probe is placed on  $s_i^k$  as well as on some  $s_x^{k'}$  such that  $\exists \{j, y\} : r_{x,y}^{k'} = r_{i,j}^k$ , then the set  $\{a_i^k, b_i^k, a_x^{k'}, b_x^{k'}, b_y^k, b_y^{k'}\}$  is added to  $\mathcal{X}$ . With the same argument as before, this also adds only two shares per input to  $\mathcal{X}$  (using two probes). In the last case, a probe is placed on some  $u_{i,j}^k$  but not on some  $s_x^{k'}$  containing the same random value. In this case, only  $\{a_i^k, b_j^k\}$  is added to  $\mathcal{X}$ . The argumentation holds for any number of probes placed on values containing the same randomness, as all inputs are independent of each other (Property 1 from Definition 11) and two probes placed on values containing the same randomness already reveal all shares required for the actual computation. Please note, that a probe placed on some output share (i.e.,  $c_i^k$ ) does not add any item to  $\mathcal{X}$ , as required by RMO-SNI.

We now show that the input shares contained in  $\mathcal{X}$  are sufficient to simulate the probes  $\mathcal{P}_{\mathcal{I}} \cup \mathcal{P}_{\mathcal{O}}$ . For this, we compute all required intermediate values exactly as in the gadget (Algorithm 1) by replacing all values  $u_{i,j}^k$ , that can not be computed, by some fresh random value. For probes placed on output shares  $c_i^k$  where  $a_i^k, b_i^k \notin \mathcal{X}$  we ignore  $w_i^k$  and compute only the sum of the corresponding  $u_{i,j}^k, \forall j$ . This ensures that all required intermediate values  $w_i^k, u_{i,j}^k, s_i^k$  and output shares  $c_i^k$  are well defined in the simulator.

Finally, in order to prove Theorem 2, we only need to show that the above defined simulator has the same output distribution for the probes  $\mathcal{P}_{\mathcal{I}} \cup \mathcal{P}_{\mathcal{O}}$  as a computation of the probes with Algorithm 1. This is true for the following reason. All intermediate values are computed exactly the same for both the simulator and Algorithm 1, except for some  $u_{i,j}^k$  which are replaced by fresh random values, and some output shares  $c_i^k$ .

Let us assume we replace some  $u_{i,j}^k$  with randomness, then this value is not directly probed, as otherwise  $a_i^k, b_j^k \in \mathcal{X}$  according to Algorithm 2 and  $u_{i,j}^k$  can be computed, but a probe is placed on either  $s_i^k$  or  $c_i^k$  as those are the only values requiring  $u_{i,j}^k$ . Let us take a closer look into these cases in the following.

Case I. Assume a probe is placed on  $s_i^k$ . From Algorithm 2 it follows that  $a_i^k \in \mathcal{X}$  (Line 7), hence,  $b_j^k \notin \mathcal{X}$ , as otherwise  $u_{i,j}^k$  can be computed. From this and Algorithm 2 it also follows that  $\nexists\{k', x, y\}$  with  $r_{i,j}^k = r_{x,y}^{k'}$  such that a probe is placed on  $u_{x,y}^{k'}$  or  $s_x^{k'}$  (Line 12). If, on the one hand, there is no probe placed at any output  $c_x^{k'}$ ,  $k' \neq k$  that

contains  $r_{i,j}^k$ , then  $r_{i,j}^k$  is only observable through  $u_{i,j}^k$  (in the computation for  $s_i^k$ ) and replacing  $u_{i,j}^k$  with fresh randomness does not change the output distribution (a probe placed on  $c_i^k$  does not reveal any additional information to  $s_i^k$ ). If, on the other hand, a probe is placed on some  $c_x^{k'}, k' \neq k$  that also contains  $r_{i,j}^k$ , then  $c_x^{k'}$  also contains t-1other random values. From Definition 12 it follows that any two probes placed in different gadgets can have at most one random value in common. As there is no other internal probe containing  $r_{i,j}^k$  and again as  $b_j^k \notin \mathcal{X}$ , there is no probe on  $s_x^{k'}$ , which is the only value sharing more than one random value with  $c_x^{k'}$ . Hence, t-1 more probes are required to remove all uniform random behavior from  $c_x^{k'}$ , but only t-2 probes are left. Therefore,  $r_{i,j}^k$  is still only observable through  $u_{i,j}^k$  and replacing  $u_{i,j}^k$  with fresh randomness does not change the output distribution.

Case II. Now, assume a probe is placed on  $c_i^k$ . If there is some probe placed on some  $s_x^{k'}$  which contains  $r_{i,j}^k$ , we can use the argumentation of Case I. Therefore, we assume only probes on output shares containing the randomness  $r_{i,j}^k$ . If  $c_i^k$  is the only output depending on  $r_{i,j}^k$ , this random value is only observable through  $u_{i,j}^k$  and replacing  $u_{i,j}^k$  with fresh randomness does not change the output distribution. If there are at least two output probes that contain  $r_{i,j}^k$  then again we require t-1 probes to remove all uniform random behavior from  $c_i^k$  but only t-2 probes are left. Hence,  $r_{i,j}^k$  is not observable at all and replacing  $u_{i,j}^k$  with fresh randomness does not change the output distribution.

Therefore, replacing some  $u_{i,j}^k$  with fresh randomness does not change the output distribution of the probes  $\mathcal{P}_{\mathcal{I}} \cup \mathcal{P}_{\mathcal{O}}$ . If there is a probe placed on some  $c_i^k$ , and  $w_i^k$  cannot be computed as either  $a_i^k \notin \mathcal{C}$  or  $b_i^k \notin \mathcal{X}$ , then there are no probes placed on  $w_i^k$ , or  $s_i^k$ . Hence, there is no probe placed on a value that shares more than one random value with  $c_i^k$ , again as the only such probe would be one placed at  $s_i^k$ . Hence, t more probes are required to remove all randomness from  $c_i^k$  but only t-1 probes are left. Therefore,  $w_i^k$  has no influence on the distribution of  $c_i^k$  and removing it from the computation does not change the output distribution.

We conclude that the simulator is able to fully simulate Algorithm 1 with input shares  $\mathcal{X}$ , which proves Theorem 2.

We emphasize that the resulting cluster is RMO-SNI and hence, special care needs to be taken when composing gadgets belonging to different clusters. We envision the usage of this approach during optimization of an already-secure design, where the clusters can be selected such that the required composition properties hold (given in Definition 11). As a result, this transformation leads to an overall design that is at most RMO-SNI. Hence, probing secure and NI secure designs will maintain their properties, but SNI designs are potentially weakened. To maintain SNI security, it is necessary to ensure that on the path from each output of a cluster to an output of the circuit, there is at least one SNI gadget.

### 3.2 Relaxed Clustering of DOM Gadgets

In Definition 11, we used a strong notion of clustering that requires an information flow analysis for both the inputs and the outputs of each gadget. The resulting small clusters offer high potential for randomness optimization, i.e., all randomness bits can be potentially reused, but also have the potential of weakening the notion of composition, i.e., RMO-SNI instead of MO-SNI. A cluster that sustains the stronger notion of MO-SNI can be built by adding more restrictions to the randomness reuse within the cluster. In particular, some randomness is required to be unique, hiding randomness being reused at the outputs. More specifically, we need to ensure that the only combination of probes that can remove all randomness from an output share are probes placed on all shares of that output. Then, due to the stronger notion of composition, the clustering rules can be relaxed by omitting the information flow analysis of the gadget outputs and focusing solely on the gadget inputs. More formally, only Property (1) and (2) from Definition 11 are required while Property (3) and (4) can be dropped.

**Definition 13** (Relaxed Clustering of DOM Gadgets). Let  $\mathsf{T} = (\mathcal{V}, \mathcal{E})$  be a simplified computation graph of vertices  $\mathcal{V} = \{G^0, G^1, \ldots, G^{n-1}\}$  and edges  $\mathcal{E} = \{E_{\ell}^{i,j} \mid i \in \mathcal{V}, j \in \mathcal{V}, \ell \leq t\}$ . A cluster of DOM gadgets is a set  $\mathcal{C} \subseteq \mathcal{V}$  such that:

$$\forall \{G^i, G^j\} \in \mathcal{C}^2, i \neq j \mid \nexists G \in \mathcal{V} : \exists \bar{P}^{G, G^i} \land \exists \bar{P}^{G, G^j} \tag{1}$$

$$\forall \{G^i, G^j\} \in \mathcal{C}^2, i \neq j \mid \nexists \bar{P}^{G^i, G^j} \tag{2}$$

An illustration of the relaxed clustering is given in Figure 1b. In contrast to clustering, the assignment of randomness to gadgets within a cluster is more restricted and, hence, the formal definition requires additional properties compared to Definition 12.

**Definition 14** (MO-SNI-Randomness Assignment). Given a cluster C as defined in Definition 13, for all DOM gadgets  $G^k \in C$  random elements can be assigned to  $G^k$  as long as the following conditions hold:

$$\forall k, \forall \{r_i, r_j\} \in \mathcal{R}^k \mid \nexists k' \neq k : \{r_i, r_j\} \in \mathcal{R}^{k'} \tag{5}$$

$$\forall k, \forall r_i \in \hat{\mathcal{R}}^k \mid \nexists k' \neq k : r_i \in \hat{\mathcal{R}}^{k'} \lor r_i \in \mathcal{R}^{k'} \tag{6}$$

$$\exists i, \forall j \neq i \mid r_{i,j} \in \hat{\mathcal{R}}^k, \tag{7}$$

where  $\hat{\mathcal{R}}^k$  is the set of unique randomness used by gadget  $G^k$ ,  $\mathcal{R}^k$  is the set of random values used for the gadget  $G^k$ , that are potentially shared with other gadgets, and  $r_{i,j}$  is the random element blinding the cross domain (i, j), i.e., the product of shares from i and j (e.g.,  $r_{i,j}^k$  in Algorithm 1).

Intuitively, Property (6) resembles the unique usage of randomness in each gadget, Property (7) ensures that one output share is blinded completely by gadget-specific fresh randomness, ensuring that all output shares are required to remove the gadget-unique randomness of one output share, while Property (5) is already used in Definition 12 and determines how to reuse randomness between gadgets of the same cluster. Illustrative examples are given in Figure 2c and Figure 2d.

Using Definition 13 and Definition 14 together with the same DOM gadget implementation as before, we now prove MO-SNI-security of a corresponding cluster.

**Theorem 3.** clusterDOM as defined in Algorithm 1, where Definition 14 is used as a replacement for Definition 12 in Line 3, is t-MO-SNI under the glitch-robust probing model.

The only difference between Theorem 3 and Theorem 2 is the security property, i.e., MO-SNI instead of RMO-SNI, and the randomness assignment. In particular, an adversary is allowed to place  $t_2 \leq t$  probes on each output instead of  $t_2 \leq t$  for all outputs together. Now we show that the same simulator as used in the proof of Theorem 2 can be used to proof Theorem 3.

*Proof.* Assume the same simulator as used in the proof of Theorem 2. In particular, the required input shares are determined using Algorithm 2 and all values are computed exactly as in Algorithm 1, except for some  $u_{i,j}^k$  and some  $c_i^k$ . Without loss of generality, we assume that the first t-1 random values assigned to each gadget are unique to this gadget, resulting in the first output share being only masked with unique randomness while all other output shares being masked with exactly one unique random value.

As before, we restrict our analysis to probes placed on  $w_i^k$ ,  $u_{i,j}^k$ ,  $s_i^k$ , and  $c_i^k$ , as other probes are strictly less powerful. Again, we need to show that the above defined simulator results in the same output distribution for the probes  $\mathcal{P}_{\mathcal{I}} \cup \mathcal{P}_{\mathcal{O}}$  as the computation of the probes with Algorithm 1. The only values computed differently in the simulator and Algorithm 1 are some  $u_{i,j}^k$  and  $c_i^k$ .

Recall, that if some value  $u_{i,j}^k$  is replaced by randomness, then there is a probe placed on either  $s_i^k$  or  $c_i^k$ , as those are the only values requiring the value  $u_{i,j}^k$ .

Case I. Assume  $s_i^k$  is probed. If this (and optionally a probe on  $c_i^k$ , which gives no additional information) is the only probe containing  $r_{i,j}^k$ , then this random value is observable only through  $u_{i,j}^k$  and the output distribution does not change by replacing  $u_{i,j}^k$  with fresh randomness. If  $\exists \{k' \neq k, x, y\} : r_{i,j}^k = r_{x,y}^{k'}$ , and a probe is placed on  $c_x^{k'}$ , then it follows from Property (7) that  $c_x^{k'}$  also contains some random value unique to the k'-th gadget. Removing the masking with a random value which is unique to the gadget, requires either some internal probe (e.g., the randomness itself) or a probe on  $c_0^{k'}$ , which itself is masked with t-2 additional random values unique to the gadget. Removing them requires either one internal probe (e.g.,  $s_0^{k'}$ ) or all other output shares. Hence, removing some gadget's unique randomness from an output share requires either some internal probe or all t + 1 shares of that particular output, where the later is prohibited by the number of available probes for each output ( $\leq t$ ). In addition to the gadget's unique randomness,  $c_x^{k'}$  also contains t-2 random values that are potentially shared with other gadgets. Property (5) ensures that two different gadgets do not share more than one random value. Hence, the only value sharing more than one random value with  $c_x^{k'}$  is  $s_x^{k'}$ , where no probe is placed as otherwise  $a_i^k \in \mathcal{X}$  (Line 6 in Algorithm 2) and  $b_j^k \in \mathcal{X}$  (Line 11 in Algorithm 2) which means  $u_{i,j}^k$  can be computed. Therefore, at least one additional probe is required to remove one reused random value in  $c_x^{k'}$ . This probe can either be an internal probe or an output probe, which itself is masked by some unique randomness different to the unique randomness in  $c_x^{k'}$ . Therefore, to remove all random behavior except  $r_{i,j}^k$  from  $c_x^{k'}$  at least t-1 probes are required, but only at most t-2 probes are left to the adversary, since there is already a probe on  $s_i^k$  and  $c_x^{k'}$ . Hence, the randomness  $r_{i,j}^k$  is observable only through  $u_{i,j}^k$  in  $s_i^k$  and replacing  $u_{i,j}^k$  with fresh randomness does not change the output distribution.

*Case II.* Now, assume a probe placed on  $c_i^k$  and  $r_{i,j}^k$  is only captured by probes on outputs. If there is a probe on some  $s_x^{k'}$  such that  $r_{i,j}^k = r_{x,y}^{k'}$ , then the arguments from Case I hold. If  $c_i^k$  is the only output probe containing  $r_{i,j}^k$ , then this random value is observable only through  $u_{i,j}^k$  and replacing that value by fresh randomness does not change the output distribution. If  $\exists \{k' \neq k, x, y\} : r_{i,j}^k = r_{x,y}^{k'}$  and a probe is placed on  $c_x^{k'}$ , then  $c_i^k$  and  $c_x^{k'}$  share at most one random value  $(r_{i,j}^k)$ , due to Property (5), while both contain at least one gadget-unique random value and t-2 random values potentially shared with other gadgets. Removing the random behavior of one of the two outputs requires t-1 internal probes (with the same argument as above) but at most t-2 probes are left to the adversary, since  $c_i^k$  and  $c_x^{k'}$  are already probed. Hence, the randomness  $r_{i,j}^k$  is not observable at all and replacing  $u_{i,j}^k$  by fresh randomness does not change the output distribution.

In conclusion,  $u_{i,j}^k$  can be perfectly simulated by a random value. Now, assume a probe placed on some  $c_i^k$ , where  $w_i^k$  can not be computed, i.e., either  $a_i^k \notin \mathcal{X}$  or  $b_i^k \notin \mathcal{X}$ . From Line 6 in Algorithm 2 follows that there is no probe placed on  $s_i^k$ , which is the only value sharing more than one random value with  $c_i^k$ . Hence, with the same argument as above, t internal probes are required to remove all random behavior from  $c_i^k$  but only t-1 probes are left to the adversary. Therefore,  $w_i^k$  is not observable and ignoring it during computation of  $c_i^k$  does not change the distribution.

We conclude, that the simulator fully simulates  $\mathcal{P}_{\mathcal{I}} \cup \mathcal{P}_{\mathcal{O}}$  which proves Theorem 3.  $\Box$

Note, however, that this optimization does not change the security properties of the original circuit, as the cluster remains MO-SNI.

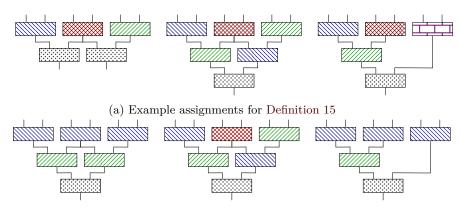

(b) Example assignments for Definition 17

Figure 3: Example assignments in different clusters, where nodes represents an  $HPC_2$  gadget. Matching colors and fill patterns resemble gadgets belonging to the same cluster. The graphs represent the simplified computation tree (here equal to the computation tree) where all edges are represented unshared.

## 4 Randomness Reduction in HPC<sub>2</sub> Composition

As the second notion of composition, we consider PINI. Again, we first discuss how gadgets can be clustered in the context of PINI, i.e., within designs composed from  $HPC_2$  gadgets [CGLS21], before we show how to reuse randomness within such clusters.

### 4.1 Clustering HPC<sub>2</sub> Gadgets.

In contrast to SNI, the essential property of PINI is the isolation of leakage within share domains, i.e., one probe can only cause the leakage of values within one share domain. As this must also hold for cross-gadget leakage caused by shared randomness, gadgets within one cluster are now allowed to have dependent inputs, effectively removing the requirement of Property (1). At the same time, a probe propagating through the design, using different paths but reaching the same gadget output, always results in only one probed output share, i.e., at the share index, the actual probe was placed. Hence, Property (4) is obsolete in the context of PINI. This results in the following formal definition:

**Definition 15** (Clustering of HPC<sub>2</sub> Gadgets). Let  $T = (\mathcal{V}, \mathcal{E})$  be a simplified computation tree of vertices  $\mathcal{V} = \{G^0, G^1, ..., G^{n-1}\}$  and edges  $\mathcal{E} = \{E_{\ell}^{i,j} \mid i \in \mathcal{V}, j \in \mathcal{V}, \ell \leq t\}$ . A cluster of HPC<sub>2</sub> gadgets is a set  $\mathcal{C} \subseteq \mathcal{V}$  such that:

$$\forall \{G^i, G^j\} \in C^2, i \neq j \mid \nexists \bar{P}^{G^i, G^j} \tag{2}$$

$$\forall \{G^i, G^j\} \in C^2, i \neq j \mid \nexists G \in \mathcal{V} : \exists \bar{P}^{G^j, G} \land \exists \bar{P}^{G^i, G} \tag{3}$$

As in Definition 11, Property (2) ensures that gadgets within one cluster are independent of each other, while Property (3) guarantees that one probe cannot propagate to multiple probes at the outputs of the cluster.

We emphasize that PINI does not enforce a refreshing layer rendering the gadget output independent of the input and, hence, due to Property (3), PINI gadgets from the same path in the computation tree cannot be clustered together. The clustering can still be done based on a simplified computation tree, however, a PINI gadget does not split a path on its own.

Again, such a cluster can have at most t (propagated-)probes at outputs of the cluster, meaning that the cluster requires to be R-PINI only, instead of PINI, for probing security.

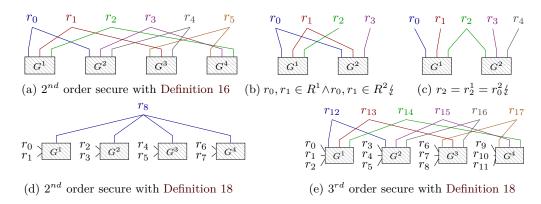

Figure 4: Example of randomness assignment for clusters of HPC<sub>2</sub> gadgets, where (4e) represents a valid assignment. The assignment in (4b) is insecure, as the pair of randomness  $\{r_0, r_1\}$  is used both in  $G^1$  and  $G^2$ , and the assignment in (4c) is insecure as  $r_2$  is used both in position 2 and 0. In (4e) and (4e) a secure assignment with gadget unique randomness for  $2^{nd}$  and  $3^{rd}$  order security is shown.

**Theorem 4.** Let  $T = (\mathcal{V}, \mathcal{E})$  be a simplified computation tree with gadgets in  $\mathcal{V}$  that are *t*-PINI and let  $\mathcal{C}$  be a cluster according to Definition 15. Further, let  $\mathcal{P}$  be a set of probes on  $\mathcal{V}$  and  $\mathcal{E}$ , with  $|\mathcal{P}| \leq t$ . Then there are at most *t* probes at output shares of  $\mathcal{C}$  including probe propagation and glitch extension of probes.

The corresponding proof follows the same line of arguments as the proof of Theorem 1 with only straight-forward changes related to PINI. Hence, we omit the proof for brevity.

**Randomness Distribution for HPC<sub>2</sub>.** The distribution of randomness within clusters of HPC<sub>2</sub> gadgets is a bit more complex than in the case of DOM. First, the same rule as for DOM is required, namely that no pair of random elements  $\{r_i, r_j\}$  is used in more than one gadget. In addition, PINI requires that random elements always mask the same share indices, i.e., are used at the same position within all gadgets that use this random element. This ensures the isolation of share domains even for cross-gadget leakage. We provide illustrative examples of secure and insecure randomness reuse for HPC<sub>2</sub> clusters in Figure 4 (first row) and define the property more formally as follows:

**Definition 16** (R-PINI-Randomness Assignment). Given a cluster C as defined in Definition 15, for all HPC<sub>2</sub> gadgets  $G^k \in C$ , random elements can be assigned arbitrarily to  $G^k$  as long as the following conditions hold:

$$\forall k, \forall \{r_i, r_j\} \in \mathcal{R}^k \mid \nexists k' \neq k : \{r_i, r_j\} \in \mathcal{R}^{k'}$$

(5)

$$\forall \{k, i, x\} : r_i^k = r_x \mid \nexists \{k', j\}, k' \neq k, j \neq i : r_j^{k'} = r_x, \tag{8}$$

where  $r_x$  is the *x*'th randomness element overall,  $r_i^k$  is the *i*'th random element assigned to gadget  $G^k$ , and  $\mathcal{R}^k$  is the set of random elements assigned to the gadget  $G^k$ .

Here, Property (5) is already used in Definition 12 and ensures that no two gadgets share more than one random element. In contrast, Property (8) is PINI specific, restricting the position of reused randomness within each gadget. More precisely, a random bit can only be reused to blind identical share domains. This ensures that cross-gadget leakage also adheres to the PINI definition.

**Security Proof.** We now prove that this rule ensures t-R-PINI for a cluster of HPC<sub>2</sub> gadgets, of which a description is given in Algorithm 3.

Algorithm 3: A single cluster, containing  $n \text{ HPC}_2$  gadgets, with reduced randomness (equal to Figure 5 in [CGLS21] for n = 1).

1 function clusterHPC<sub>2</sub> ( $(a^0, b^0), ..., (a^{n-1}, b^{n-1})$ ): **Require:**  $t \ge 2$  **Require:**  $a^k, b^k \in \mathbb{F}_2^{t+1}$  such that  $a^k : (a_0^k, \dots, a_t^k), b^k : (b_0^k, \dots, b_t^k)$  with  $\sum_j a_j^k = a^k$ and  $\sum_{j} b_{j}^{k} = b^{k}$ // Initialize randomness for k = 0 to n - 1 do  $\mathbf{2}$  $R^k = \langle r_0^k, \dots, r_{m-1}^k \rangle \leftarrow \text{Distribution according to Definition 16}$ 3  $q \leftarrow 0$ 4 5 for i = 0 to t do for j = i + 1 to t do 6  $\begin{array}{c} \tilde{r}_{i,j}^k \leftarrow r_q^k; \ r_{j,i}^k \leftarrow r_q^k \\ q \leftarrow q+1 \end{array}$ 7 8 // Compute  $HPC_2$  gadgets for k = 0 to n - 1 do 9 for i = 0 to t do 10  $w_i^k \gets a_i^k \cdot \texttt{Reg}[b_i^k]$ 11  $\begin{array}{c} \mathbf{w}_{i} \leftarrow u_{i} + \operatorname{Reg}[v_{i}] \\ \mathbf{for} \ j = 0 \ to \ t, j \neq i \ \mathbf{do} \\ u_{i,j}^{k} \leftarrow (a_{i}^{k} + 1) \cdot \operatorname{Reg}[r_{i,j}^{k}] \\ v_{i,j}^{k} \leftarrow b_{j}^{k} + r_{i,j}^{k} \\ z_{i,j}^{k} \leftarrow a_{i}^{k} \cdot \operatorname{Reg}[v_{i,j}^{k}] \end{array}$ 12 13 14 15  $\begin{array}{c} \stackrel{-}{\text{for }}i=0 \ to \ t \ \textbf{do} \\ \big| \quad c_i^k \leftarrow \operatorname{Reg}[w_i^k] + \sum_{j=0, j \neq i}^t (\operatorname{Reg}[u_{i,j}^k] + \operatorname{Reg}[z_{i,j}^k]) \end{array}$ 16 17 **Ensures:**  $c^k : (c_0^k, \ldots, c_t^k) \in \mathbb{F}_2^{t+1}$  such that  $\sum_j c_j^k = a^k \cdot b^k, \forall k$ return  $c^0, \ldots, c^{n-1}$ 18

**Theorem 5.** clusterHPC<sub>2</sub> as defined in Algorithm 3 is t-R-PINI secure in the glitch-robust model.

Our proof follows closely the argumentation of Cassiers et al. for a single  $\mathsf{HPC}_2$  gadget [CGLS21].

Proof. Let us denote a set of internal probes  $\mathcal{P}_{\mathcal{I}}$  and a set of output probes  $\mathcal{P}_{\mathcal{O}}$ , such that  $\mathcal{P}_{\mathcal{I}} \cup \mathcal{P}_{\mathcal{O}} \leq t$ . Without loss of generality, we restrict the probes to only capture  $c_i^k$ ,  $w_i^k$ ,  $w_{i,j}^k$ ,  $w_{i,j}^k$ , and  $z_{i,j}^k$  as other extended probes are less powerful, due to glitch extension. In Algorithm 4, we give an algorithm that, given the set of probes  $\mathcal{P}_{\mathcal{I}} \cup \mathcal{P}_{\mathcal{O}}$ , returns a set of input shares  $\mathcal{X}$  required to simulate the probes for the gadget defined in Algorithm 3. In particular, Algorithm 4 returns all inputs such that all required intermediate values can be computed exactly as in Algorithm 3, except for some  $v_{i,j}^k$ . We first show that, for all possible probe placements, Algorithm 4 adds at most one share index per probe to  $\mathcal{X}$ , where the share indices of probes capturing an output are always in  $\mathcal{X}$ . Afterwards, we show that the inputs in  $\mathcal{X}$  enable a simulation of the probes  $\mathcal{P}_{\mathcal{I}} \cup \mathcal{P}_{\mathcal{O}}$ , as required for R-PINI.

From the construction of Algorithm 4 it is obvious that all probes that do not capture an output  $c_i^k$  add at most one share index to  $\mathcal{X}$ . If all probes in  $\mathcal{P}_{\mathcal{O}}$  capture different share indices then only Line 6 in Algorithm 4 is activated, which adds the respective share index to  $\mathcal{X}$ . Now, assume there are multiple probes capturing outputs of the same share index *i*. From Property (5) it follows that each pair  $\{c_i^k, c_i^{k'}\}, k \neq k'$  of such probes can have at most one random value in common and Property (8) guaranties that this random value is Algorithm 4: Input-share chooser for the simulator of clusterHPC<sub>2</sub>. (equal to the description in the proof for Proposition 4 in [CGLS21] for n = 1.)

1 function ShareChooser<sup>clusterHPC2</sup> ( $\mathcal{P}$ ):  $\mathcal{X} \leftarrow \emptyset$  $\mathbf{2}$ for i = 0 to t do 3 for k = 0 to n - 1 do 4 if  $w_i^k$  or  $c_i^k$  is probed then 5  $| \mathcal{X} \leftarrow \mathcal{X} \cup \{i\}$ 6 for j = 0 to  $t, j \neq i$  do 7  $\begin{array}{l} \text{if } u_{i,j}^k, v_{i,j}^k, \ or \ z_{i,j}^k \ is \ probed \ and \ i \in \mathcal{X} \ or \ j \in \mathcal{X} \ \textbf{then} \\ \ \left\lfloor \begin{array}{c} \mathcal{X} \leftarrow \mathcal{X} \cup \{i,j\} \end{array} \right. \end{array}$ 8 9 10 11 else if  $v_{i,j}^k$  is probed then  $\[ \mathcal{X} \leftarrow \mathcal{X} \cup \{j\} \]$ 12 13 **if** at least two probes on  $c_i^k$ ,  $c_i^{k'}$  with  $k' \neq k$  and  $r_{i,j}^k = r_{i,j}^{k'}$  **then**   $\ \ \, \mathcal{X} \leftarrow \mathcal{X} \cup \{j\}$ 14 15 return  $\mathcal{X}$ 16

used to blind the same two share indices i and j. Hence, all such probes will add the same share index i to  $\mathcal{X}$  (Line 6) and all but the first add at most one additional share index j to  $\mathcal{X}$  (Line 21). This also holds for combinations of probes capturing up to t output shares, as this can always be reduced to multiple pairs of probes which add redundant share indices to  $\mathcal{X}$ . Therefore, Algorithm 4 adds at most one share index per probe, where, for each share index i of an output captured by a probe, Line 6 guaranties  $i \in \mathcal{X}$ . We emphasize that this is not true for standard PINI, where an entire output share index is probed at once and, hence, an attacker gets combination of output probes for free.

We now show that the share indices in  $\mathcal{X}$  are sufficient to simulate the probes  $\mathcal{P}_{\mathcal{I}} \cup \mathcal{P}_{\mathcal{O}}$ . For this we compute all required intermediate values exactly as defined by the gadget (Algorithm 3) by replacing all values  $v_{i,j}^k$ , that cannot be computed by some fresh random value. Hence, all extended probes capturing  $w_i^k$ ,  $u_{i,j}^k$ , and  $v_{i,j}^k$  can be directly computed by construction of Algorithm 4, and probes capturing  $c_i^k$ , or  $z_{i,j}^k$ , where some share index  $j \notin \mathcal{X}$  exists, are computed by replacing the corresponding intermediate value  $v_{i,j}^k$  by fresh randomness.

This simulator results in the same output distribution for the probes  $\mathcal{P}_{\mathcal{I}} \cup \mathcal{P}_{\mathcal{O}}$  as a computation of the probes with Algorithm 3, for the following reason: All values are computed exactly the same for both, the simulator and Algorithm 3, except for some  $v_{i,j}^k$  which are replaced by fresh random values. Let us assume we replace some  $v_{i,j}^k$  with randomness, then it holds that either  $i \notin \mathcal{X}$  or  $j \notin \mathcal{X}$  and a value depending on  $v_{i,j}^k$  is probed  $(v_{i,j}^k, z_{i,j}^k, \text{ or } c_i^k)$ .

If a probe is placed directly on  $v_{i,j}^k$  then  $j \in \mathcal{X}$ , according to Algorithm 4, which means  $i \notin \mathcal{X}$ . Therefore, there cannot be any other probe placed on some  $u_{i,j}^{k'}$ ,  $u_{j,i}^{k'}$ ,  $v_{i,j}^{k'}$ ,  $v_{j,i}^{k'}$ ,  $z_{i,j}^{k'}$ ,  $z_{j,i}^{k'}$ ,  $c_i^{k'}$ , or  $c_j^{k'}$  for all k'. However, from Property (8) and Algorithm 3 it follows that those are the only values that can dependent on the random value  $r_{i,j}^k$ , which means  $r_{i,j}^k$  is only observable through  $v_{i,j}^k$  and replacing  $v_{i,j}^k$  with fresh randomness does not change the output distribution.

Otherwise, if a probe is placed on  $z_{i,j}^k$  or  $c_i^k$  then  $i \in \mathcal{X}$ , according to Algorithm 4,

which means  $j \notin \mathcal{X}$ . Therefore, there cannot be any other probe placed on some  $u_{j,i}^{k'}, v_{i,j}^{k'}, z_{j,i}^{k'}$ , or  $c_j^{k'}$  for all k'. Similar, there is at most one probe placed on  $u_{i,j}^{k'}, v_{j,i}^{k'}, z_{i,j}^{k'}$  or  $c_i^{k'}$ , with  $r_{i,j}^k = r_{i,j}^{k'}$ , for all k'. Again, those are all possible values dependent on  $r_{i,j}^k$  and, hence, there is exactly one probe placed on a value depending on  $r_{i,j}^k$ , which is either  $z_{i,j}^k$  or  $c_i^k$ .

Case I: Assuming there is a probe placed on  $z_{i,j}^k$ , the corresponding extended probe is  $\{a_i^k, v_{i,j}^k, z_{i,j}^k\}$ , which contains the only values through which  $r_{i,j}^k$  can be observed (with the argumentation from above). Therefore, replacing  $v_{i,j}^k$  with fresh randomness does not change the output distribution.

*Case II:* Assuming there is a probe placed on  $c_i^k$ , the only observations depending on  $r_{i,j}^k$  can be made via the extended probe of  $c_i^k$  (with the same argumentation as above), in particular, through the values  $u_{i,j}^k$  or  $z_{i,j}^k$ . If  $a_i^k = 0$ , then it holds that  $z_{i,j}^k = a_i^k \cdot v_{i,j}^k = 0$  independent of  $v_{i,j}^k$ , which means replacing  $v_{i,j}^k$  with fresh randomness is not observable. Otherwise, if  $a_i^k = 1$ , it holds that  $u_{i,j}^k = (a_i^k + 1) \cdot r_{i,j}^k = 0$  independent of  $r_{i,j}^k$ , which means  $r_{i,j}^k$  and, thus, replacing this value by fresh randomness does not change the output distribution.

Therefore, replacing some  $v_{i,j}^k$  with a random value does not change the output distribution of the probes  $\mathcal{P}_{\mathcal{I}} \cup \mathcal{P}_{\mathcal{O}}$  and, hence, the simulator is able to fully simulate Algorithm 3 with share indices in  $\mathcal{X}$ , which proves Theorem 5.

We emphasize that the resulting cluster is R-PINI which requires special care when composing gadgets belonging to different clusters. As in the case of RMO-SNI, we envision the usage during optimization of an already-secure design, where the clusters can be selected such that the required composition properties hold (given in Definition 15). This transformation leads to an overall design that is at most R-PINI, and in contrast to RMO-SNI, there is no natural way within the context of PINI to recover the PINI properties.

#### 4.2 Relaxed Clustering

The rules for clustering defined in Definition 15 are quite restrictive, especially as PINI gadgets do not split any path in the simplified computation tree. Hence, even when the defined clustering allows a high level of randomness reuse within a cluster, for most designs only small clusters can be created. This effect is even stronger than for SNI. In addition, we have a weakening of the resulting notion of composition. Unfortunately, as PINI does not stop probe propagation from outside a gadget to the inside, the clustering cannot be relaxed in the same manner for PINI-only gadgets as described in Section 3.2 for SNI. The reason is that some gadget-unique randomness cannot hide the reusable randomness completely at the outputs.

In the case of  $\text{HPC}_2$  gadgets, this can be fixed by adding a register layer at the output, effectively making the gadget SNI as well. More precisely, we add some  $d_i^k \leftarrow \text{Reg}[c_i^k]$  to the algorithm (as Line 18), which is then considered the output share *i* of the *k*'th gadget. We call this gadget version  $\text{HPC}_2^+$ .

The resulting rules for clustering and randomness reuse are similar to Definition 13 and Definition 14 but integrate the considerations made so far for HPC<sub>2</sub>. As the resulting gadget is SNI, the corresponding path is split in the simplified computation tree, and the resulting clusters are both MO-SNI and PINI, however, at the cost of additional area and latency. More formally, we can define the relaxed clustering of HPC<sub>2</sub><sup>+</sup> gadgets as follows:

**Definition 17** (Relaxed Clustering of  $HPC_2^+$  Gadgets). Let  $T = (\mathcal{V}, \mathcal{E})$  be a simplified computation tree of vertices  $\mathcal{V} = \{G^0, G^1, ..., G^{n-1}\}$  and edges  $\mathcal{E} = \{E_\ell^{i,j} \mid i \in \mathcal{V}, j \in \mathcal{V}\}$  $\mathcal{V}, \ell \leq t$ }. A cluster of  $\mathsf{HPC}_2^+$  gadgets is a set  $\mathcal{C} \subseteq \mathcal{V}$  such that:

$$\forall \{G^i, G^j\} \in \mathcal{C}^2 \mid \nexists \bar{P}^{G^i, G^j}. \tag{2}$$

Hence, only Property (2), which ensures independence of the gadgets within a cluster, is required, and all other clustering properties can be dropped. For such a clustering, we can utilize the same randomness assignment as given in Definition 14, where we additionally ensure that randomness is only reused at the same position within different gadgets, i.e., Property (8).

**Definition 18** (PINI-SNI-Randomness Assignment). Given a cluster C as defined in Definition 17, for  $HPC_2^+$  gadgets  $G^k \in \mathcal{C}$  random elements can be assigned arbitrarily to  $G^k$  as long as the following conditions hold:

$$\forall k, \forall \{r_i, r_j\} \in \mathcal{R}^k \mid \nexists k' \neq k : \{r_i, r_j\} \in \mathcal{R}^{k'} \tag{5}$$

$$\forall k, \forall r_i \in \hat{\mathcal{R}}^k \mid \nexists k' \neq k : r_i \in \hat{\mathcal{R}}^{k'} \lor r_i \in \mathcal{R}^{k'} \tag{6}$$

$$\forall r_i \in \mathcal{R}^{\kappa} \mid \nexists k' \neq k : r_i \in \mathcal{R}^{\kappa} \quad \forall r_i \in \mathcal{R}^{\kappa}$$

$$\exists i, \forall j \neq i \mid r_{i,j} \in \hat{\mathcal{R}}^k$$

$$(6)$$

$$\forall \{k, i, x\} : r_i^k = r_x \mid \nexists \{k', j\}, k' \neq k, j \neq i : r_i^{k'} = r_x, \tag{8}$$

where  $r_i$  is the *i*'th random element overall,  $r_{i,i}$  is a random element hiding share indices *i* and j,  $\hat{\mathcal{R}}^k$  is the set of unique randomness used for the gadget  $G^k$ , and  $\mathcal{R}^k$  is the set of randomness used for the gadget  $G^k$  that is potentially reused by other gadgets.

Using Definition 17 and Definition 18 together with the  $HPC_2^+$  gadget we now prove PINI for the corresponding cluster.

**Theorem 6.** cluster  $HPC_2$  as defined in Algorithm 3, where Definition 18 is used as a replacement for Definition 16 in Line 3 and an output register  $(d_i^k \leftarrow \operatorname{Reg}[c_i^k])$  is added, is t-PINI secure in the glitch-robust model.

Proof. Assume the same simulator as used in the proof of Theorem 5, where we extend Algorithm 4 such that  $\mathcal{X} \leftarrow \mathcal{X} \cup \{i\}$  when there is a probe placed on  $d_i^k$ . In particular, the simulator computes all values exactly as specified in Algorithm 3, except for some  $v_{i,j}^k$  and the extension of  $d_k^k$ . Without loss of generality, we assume the first t-1 random values assigned to each gadget are unique to this gadget, resulting in the output share index 0 being only masked with unique randomness while all other output shares being masked with exactly one unique random value.

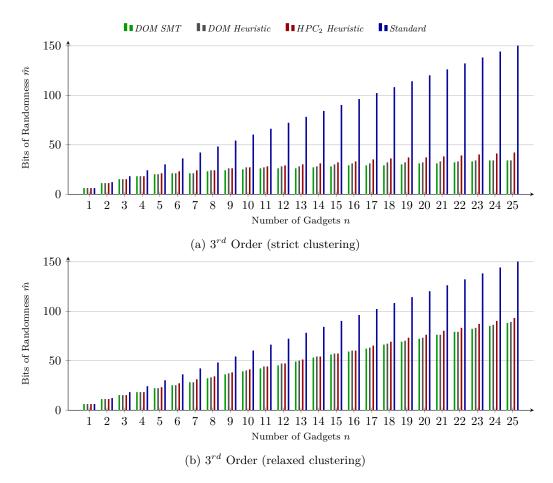

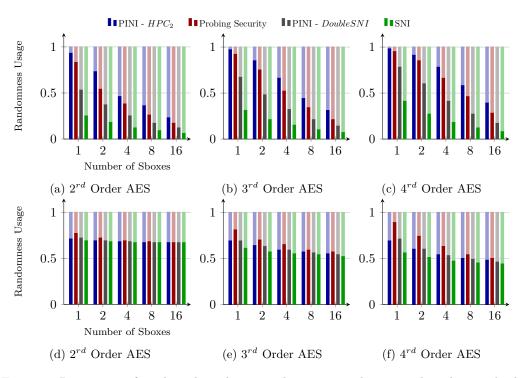

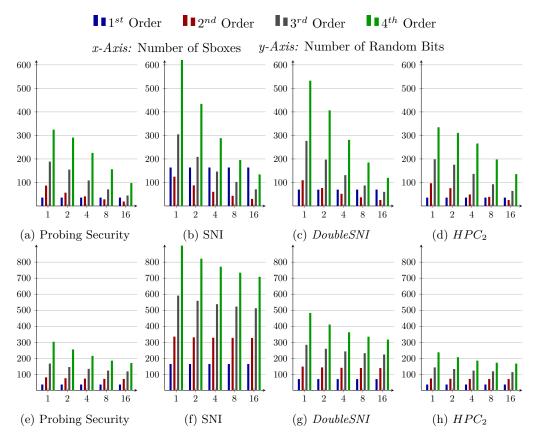

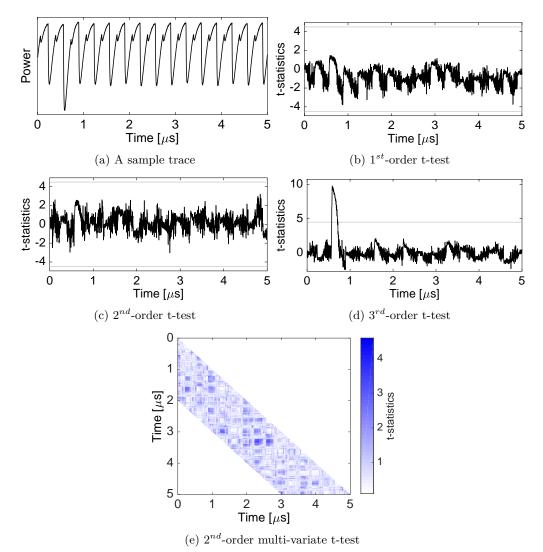

As before, we restrict our analysis to probes placed on  $w_i^k$ ,  $u_{i,j}^k$ ,  $v_{i,j}^k$ ,  $z_{i,j}^k$ ,  $c_i^k$ , as other probes only provide a subset of information. In addition, an attacker can probe an output share index i, which reveals the set  $\{d_i^{k'} \mid \forall k'\}$ . Again, we need to show that the above defined simulator results in the same output distribution for the probes  $\mathcal{P}_{\mathcal{I}} \cup \mathcal{P}_{\mathcal{O}}$  as the computation of the probes with Algorithm 3 extended by the computation of  $d_i^k$ . The only values computed differently in the simulator and Algorithm 3 are some  $v_{i,j}^k$ .